# Man computer Interactive Data Access System

**NOV 1987**

# IBM PC/AT® BASED WORKSTATION HARDWARE DESCRIPTION

· Space Solkere UW SSEC Publication No. 87.11.1

### PREFACE

This manual was prepared by the Space Science and Engineering Center (SSEC), University of Wisconsin-Madison, to assist you with hardware maintenance of the IBM PC/AT-based Man-computer Interactive Data Access System (McIDAS) workstation.

This manual specifically covers IBM PC/AT-based workstations built since late 1986. Older McIDAS workstations that have been upgraded with an IBM PC/AT may contain several circuit boards (TV Timing, 12-Bit Colorizer, and Joystick) that are different than those described in this manual. Owners of workstations built prior to late 1986 should have received, or should request two copies of the McIDAS Workstation Hardware Description and Appendix B - McIDAS Workstation Hardware Schematics and Assembly Drawings; this documentation should be retained if any of your workstations have been upgraded. If there is a question of documentation applicability, check circuit board modification levels against the modification level cited on the first page of each section of your hardware reference manual(s).

In each workstation, some units are off-the-shelf devices, while others are designed and developed by SSEC. This manual is designed to provide primary documentation for SSEC-developed units and to complement off-the-shelf unit documentation. Therefore, an important part of this manual is a list of reference manuals you should have received with your McIDAS. Appendix A is a typical McIDAS reference manual list.

A brief system overview and detailed workstation overview are followed by unit or circuit board documentation. Each unit or circuit board section includes an introduction, a functional description, and either applicable references for off-the-shelf units or detailed circuit descriptions for custom units.

# TABLE OF CONTENTS

| SECTION 1: McIDAS WORKSTATION OVERVIEW            |          |

|---------------------------------------------------|----------|

| Introduction                                      | 1-1      |

| McIDAS System Description                         | 1-1      |

| McIDAS Workstation Description                    | 1-4      |

| Electronic Control Cabinet (Tower) Overview       | 1-9      |

| SECTION 2: SINGLE BOARD COMPUTER Introduction     | 2-1      |

| Hardware Functional Description                   |          |

| Microprocessor                                    |          |

| Memory and I/O Mapping                            |          |

| EPROM.                                            |          |

| RAM.                                              |          |

| Serial I/O Interface                              | 2 2 2    |

| General Purpose Timer                             | E. E. E. |

| Parallel I/O Interface                            |          |

| Interrupt Controller                              |          |

| interrupt controller                              | 2-0      |

| SECTION 3: DUAL CHANNEL COLORIZER                 |          |

| Introduction                                      | 3-1      |

| Functional Description                            |          |

| Detailed Circuit Description                      |          |

| Schematic Conventions                             | 3-4      |

| Control Logic                                     | 3-4      |

| Image Data Input Unit                             |          |

| Decompression Unit                                | 3-9      |

| Mask Logic Unit                                   |          |

| Mask Control Register                             |          |

| Bus Multiplexer                                   |          |

| RAM Enhancement Table                             |          |

| RGB Bus Controller                                | 3-14     |

| SECTION 4: 50-60 HZ TV TIMING AND COLORIZER BOARD |          |

| Introduction                                      | 4-1      |

| Functional Description                            |          |

| TV Timing Unit                                    |          |

| Graphics/Cursor Colorizer Unit                    |          |

| Detailed Circuit Description                      |          |

| TV Timing Unit                                    |          |

| Graphics/Cursor Colorizer Unit                    |          |

|                                                   |          |

| SECTION 5: CURSOR GENERATOR                       |          |

| Introduction                                      |          |

| Functional Description                            |          |

| Cursor Generator Functional Description           |          |

| Joystick Support Interface Functional Description |          |

| Detailed Circuit Description                      |          |

| Shared Circuits Description                       |          |

| Cursor Generator Circuit Description              |          |

| Joystick Support Interface Circuit Description    | 5-18     |

| SECTION 6: DATARAM CONTROL BOARD                     |          |

|------------------------------------------------------|----------|

|                                                      | -1       |

| Functional Description 6-                            | -2       |

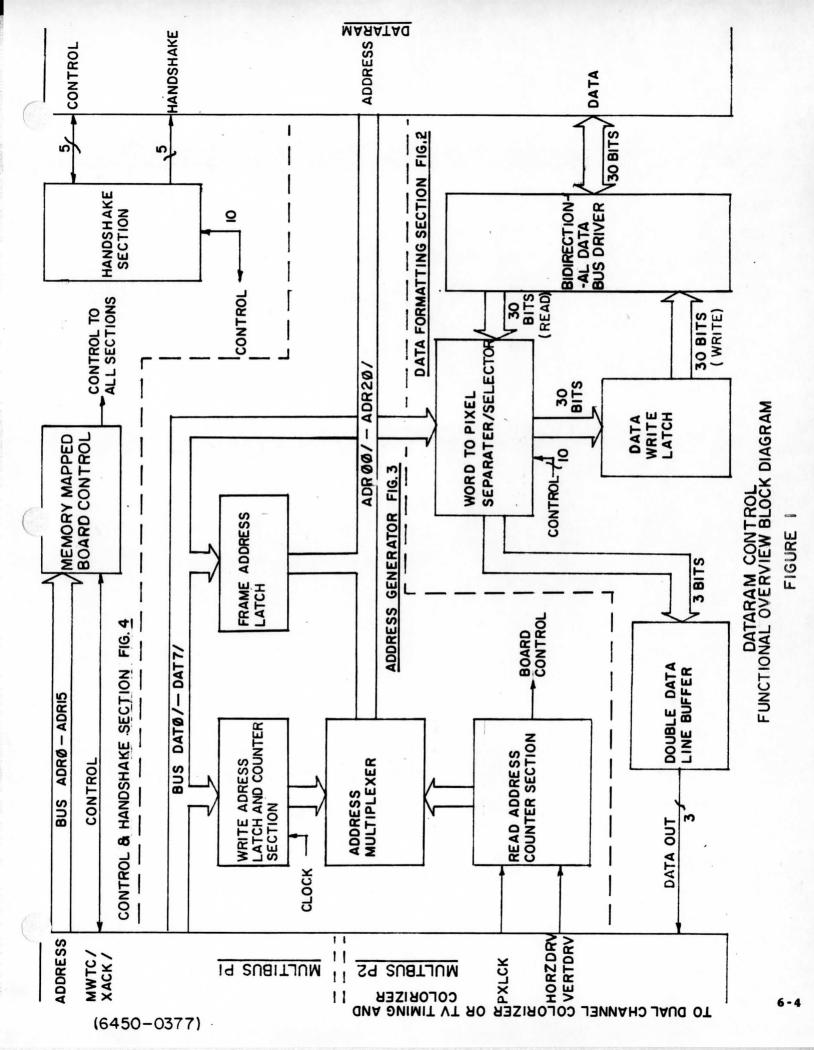

| Overview 6-                                          |          |

| Detailed Functional Description6-                    | -7       |

|                                                      | -7       |

|                                                      | -1       |

|                                                      | -1       |

|                                                      | -1       |

|                                                      | -1       |

|                                                      |          |

|                                                      | -1       |

|                                                      | -18      |

|                                                      | -18      |

| DATARAM Address and Line Buffer Address Generator 6- |          |

| Control and Handshake 6-                             | -3       |

|                                                      |          |

| SECTION 7: DATARAM/MULTIBUS INTERFACE                |          |

| Introduction 7-                                      | -1       |

|                                                      | -1       |

|                                                      | -1       |

|                                                      | -3       |

|                                                      | -3       |

|                                                      | -3       |

|                                                      | -3       |

|                                                      | -3<br>-4 |

|                                                      | -4<br>-4 |

|                                                      | -4<br>-4 |

|                                                      |          |

| MULTIBUS Control Repeater                            |          |

| Address and Data Bus Repeaters                       | -4       |

| Transfer Acknowledge Generator                       |          |

| Video Repeater 7-                                    | -5       |

|                                                      |          |

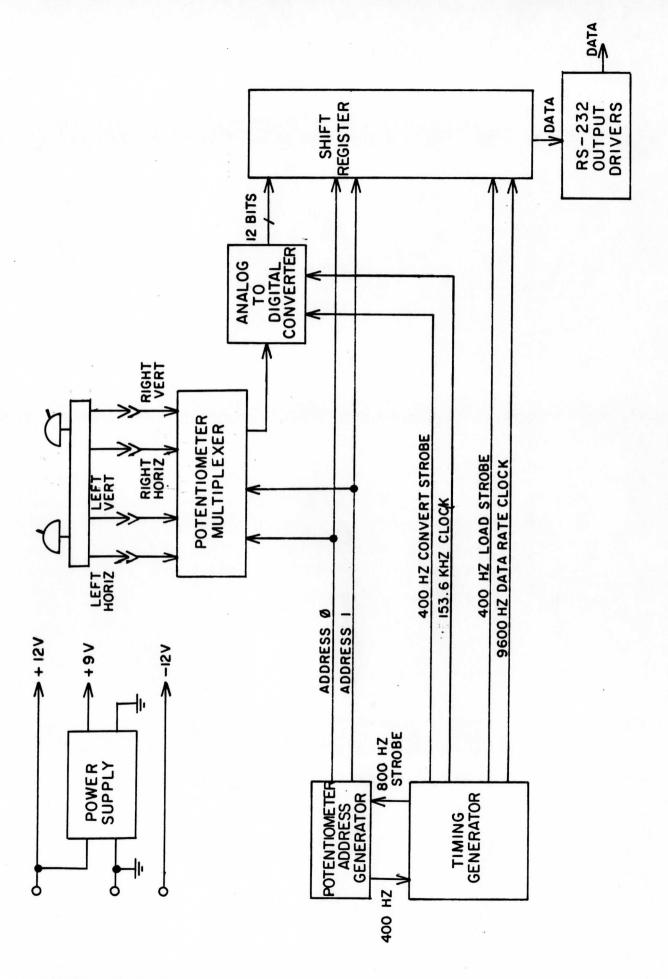

| SECTION 8: DIGITAL JOYSTICK 2                        |          |

| Introduction 8-                                      | -1       |

| Functional Description 8-                            | -1       |

| Detailed Circuit Description 8-                      |          |

| Schematic Conventions 8-                             |          |

| Baud Rate Generator 8-                               |          |

| Pot Address Generator 8-                             | -4       |

| Pot Multiplexer8-                                    |          |

| Analog-to-Digital Converter8-                        |          |

| Shift Register8-                                     |          |

| RS-232 Output Drivers8-                              |          |

| Power Supplies8-                                     |          |

| rower supplies o-                                    | -0       |

| GROWING DAY (VINGO) MY GUNG BOARD                    |          |

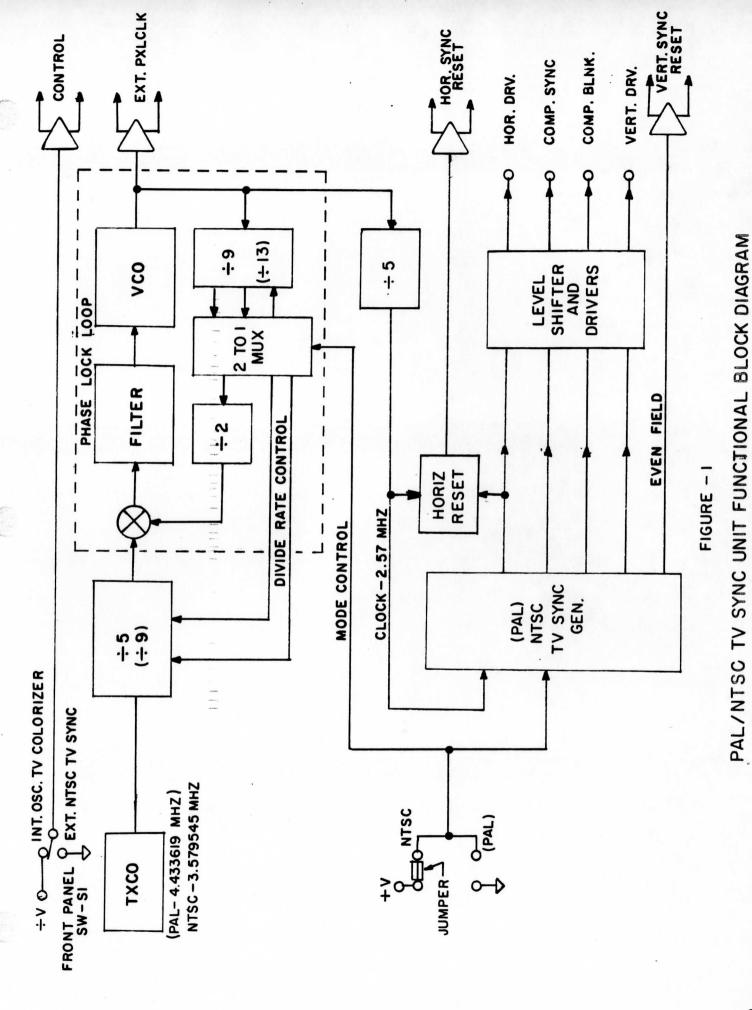

| SECTION 9: PAL (NTSC) TV SYNC BOARD                  |          |

| Introduction9-                                       | _        |

| Functional Description9-                             | _        |

| Detailed Circuit Description 9-                      |          |

| Schematic Conventions 9-                             |          |

| Mode Control Multiplexer9-                           |          |

| TXCO Oscillator 9-                                   | -5       |

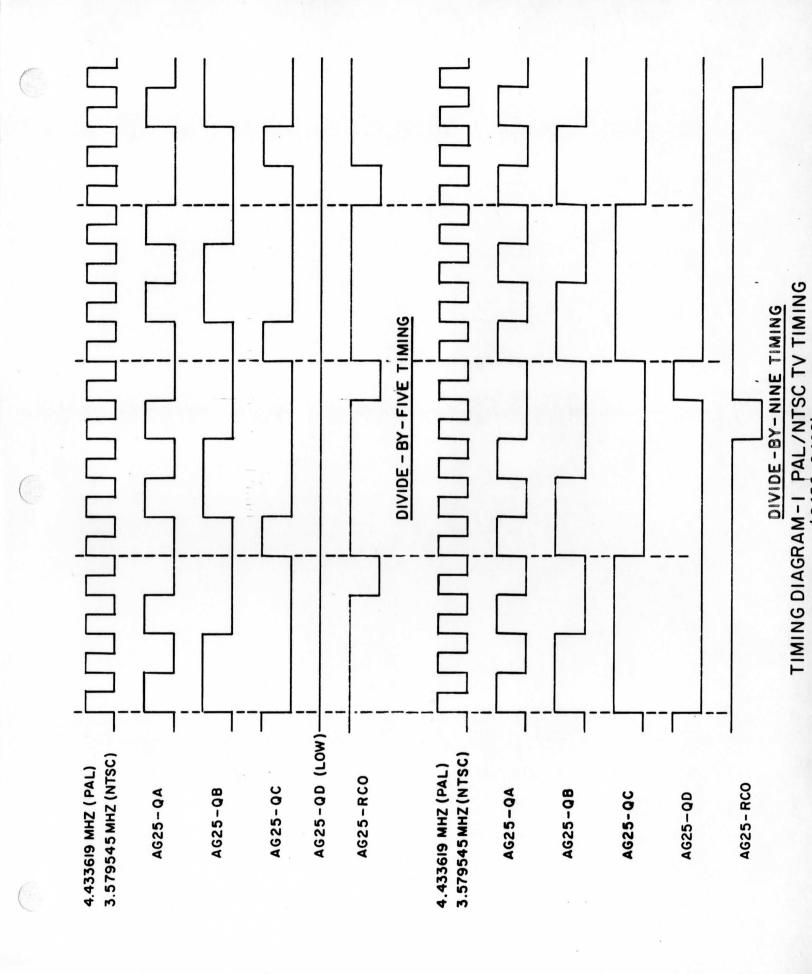

| Divide-by-Five/Nine Circuit9-                        | -6       |

|             | e Comparator                                 |      |

|-------------|----------------------------------------------|------|

|             | er                                           |      |

|             |                                              |      |

|             | de-by-Nine/Thirteen Circuit                  |      |

|             | de-by-Two Circuit                            |      |

|             | TV Sync Generator                            |      |

|             | de-by-Five                                   |      |

|             | 1 Shifters and Drivers                       |      |

| Reset       | t Generator                                  | 9-12 |

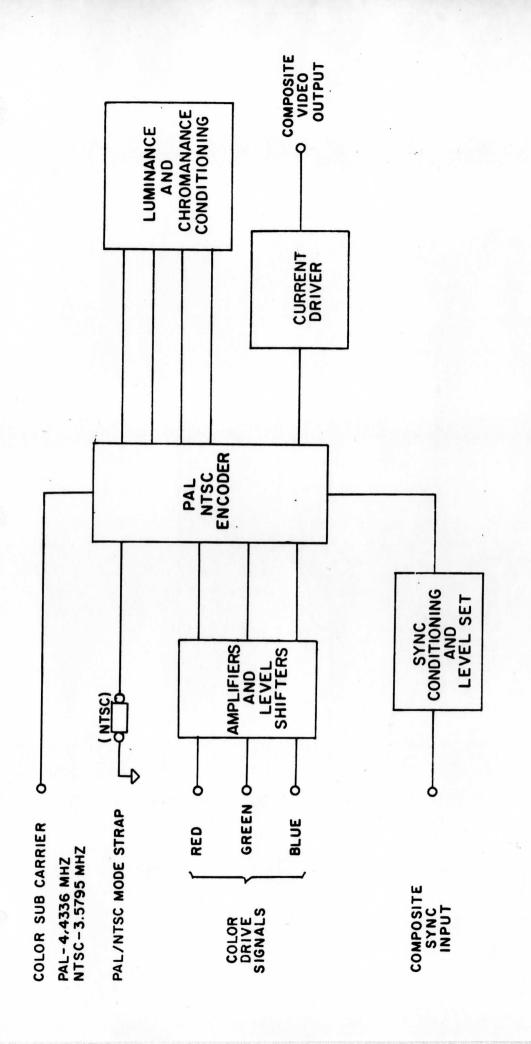

| SECTION 10: | PAL/NTSC BOARD                               |      |

|             | ion                                          | 10-1 |

|             | 1 Description                                |      |

|             | Circuit Description                          |      |

|             | matic Conventions                            |      |

| Color       | r Drive Amplifiersl                          | 10-3 |

| Sync        | Conditioning and Level Set Circuitry         | 10-3 |

| Lumin       | nance and Chrominance Conditioning Circuitry | 10-4 |

| RGB (       | Color to PAL/NTSC Encoder                    | .0-5 |

| APPENDIX A: | LIST OF REFERENCES                           |      |

| APPENDIX B: | SCHEMATIC DIAGRAMS (separate)                |      |

|             | SUPPLEMENTAL INFORMATION FOR PAL/NTSC TV     |      |

# FIGURES AND TIMING DIAGRAMS

| SECTION 1: McIDAS WORKSTATION OVERVIEW  Figure 1 - McIDAS System Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-5<br>1-10                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| SECTION 2: SINGLE BOARD COMPUTER Figure 1 - Microprocessor Board Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-3                                                 |

| SECTION 3: DUAL CHANNEL COLORIZER  Figure 1 - Dual Channel Colorizer Block Diagram  Timing Diagram 1 - Control Signals  Table 1 - Decompression PROM State Table                                                                                                                                                                                                                                                                                                                                              | 3-6                                                 |

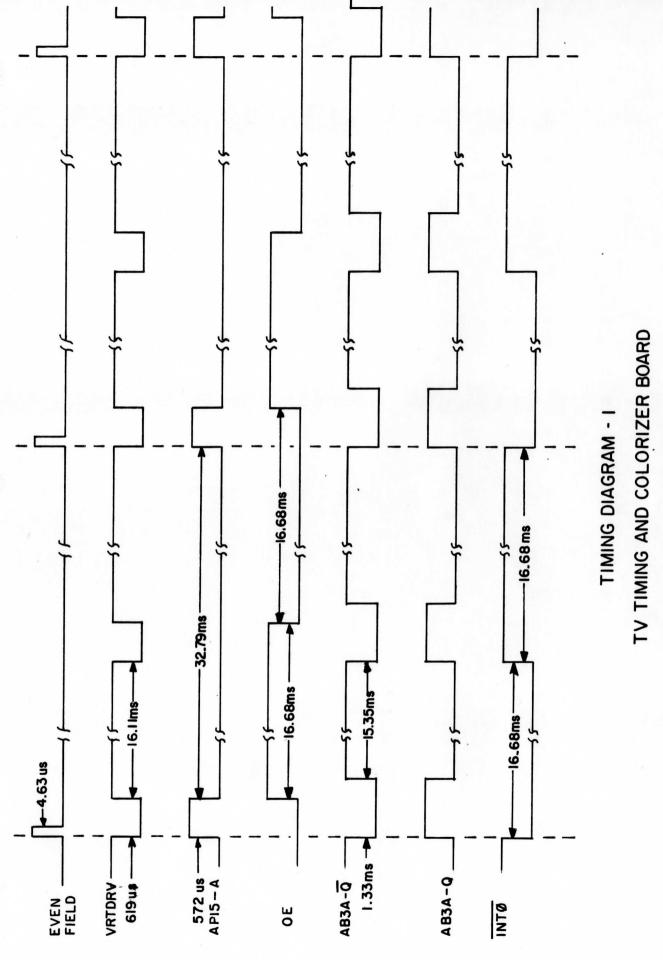

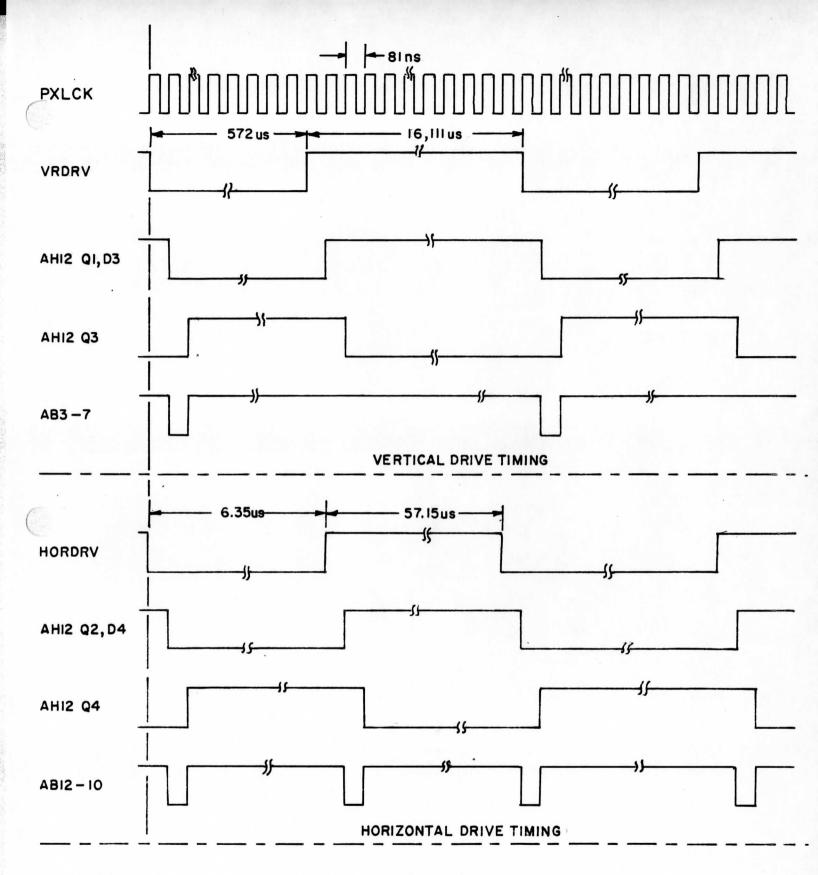

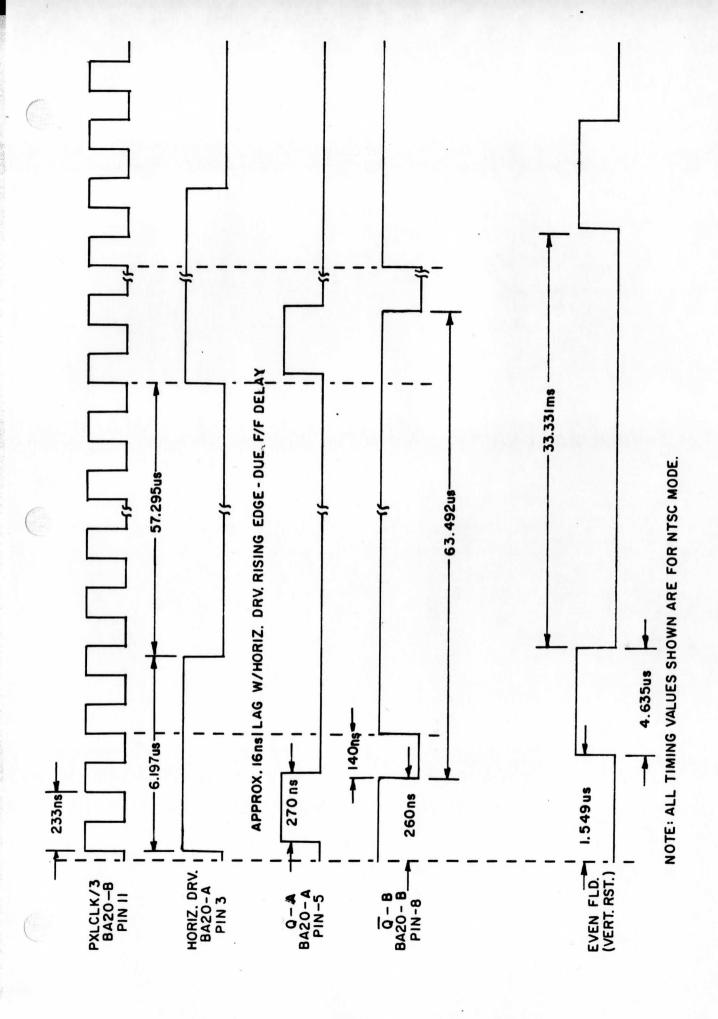

| SECTION 4: TV TIMING AND COLORIZER BOARD  Figure 1 - TV Timing Generator Block Diagram  Figure 2 - Graphics/Cursor Colorizer Block Diagram  Timing Diagram 1 - TV Timing and Colorizer Board                                                                                                                                                                                                                                                                                                                  | 4-5                                                 |

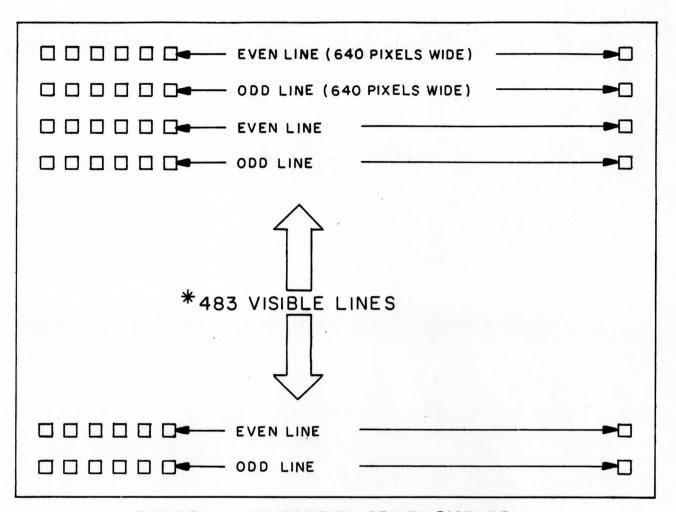

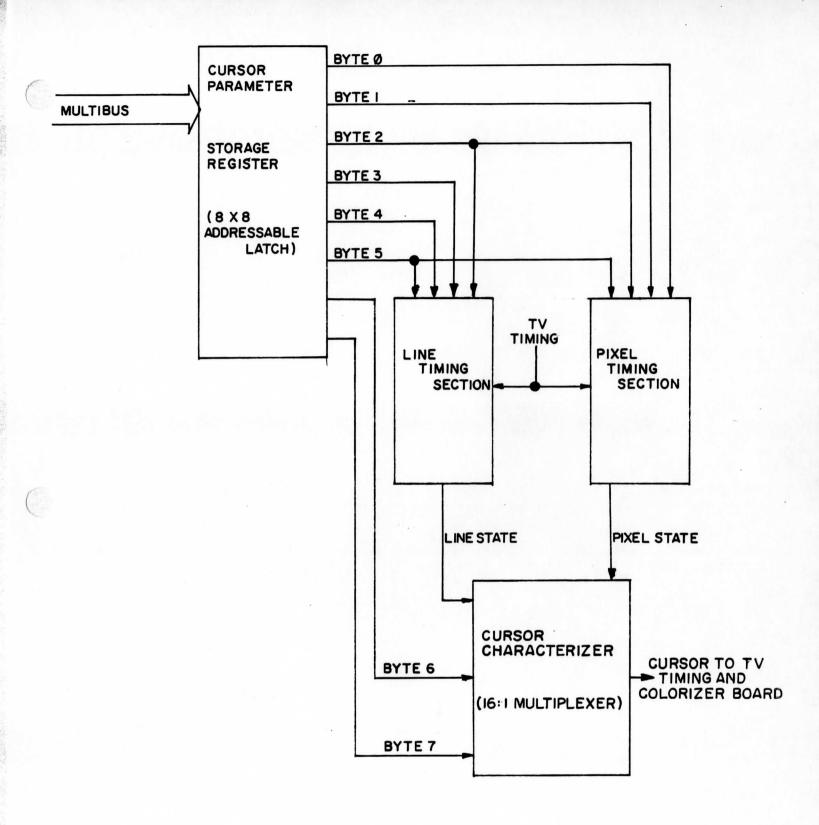

| SECTION 5: CURSOR GENERATOR  Figure 1 - Composition of a Digital TV Picture                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-5<br>5-7<br>5-14<br>5-16<br>5-19<br>5-23          |

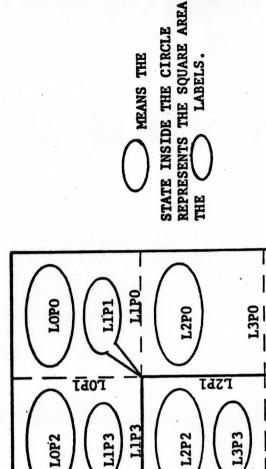

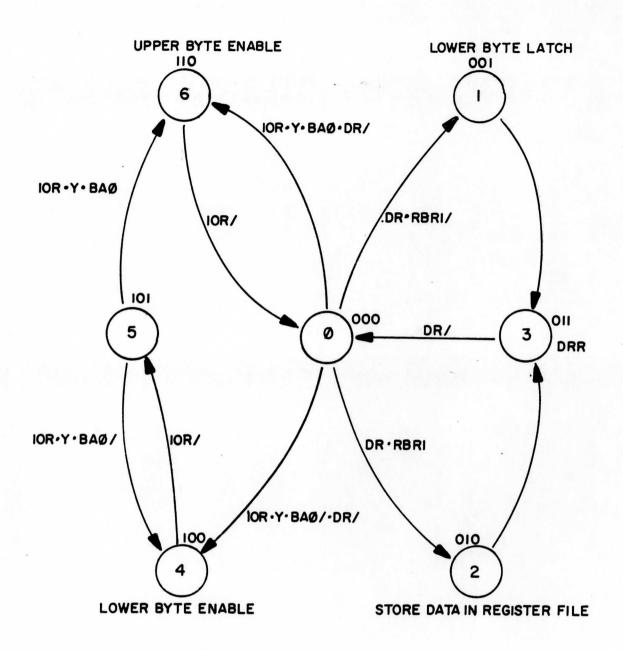

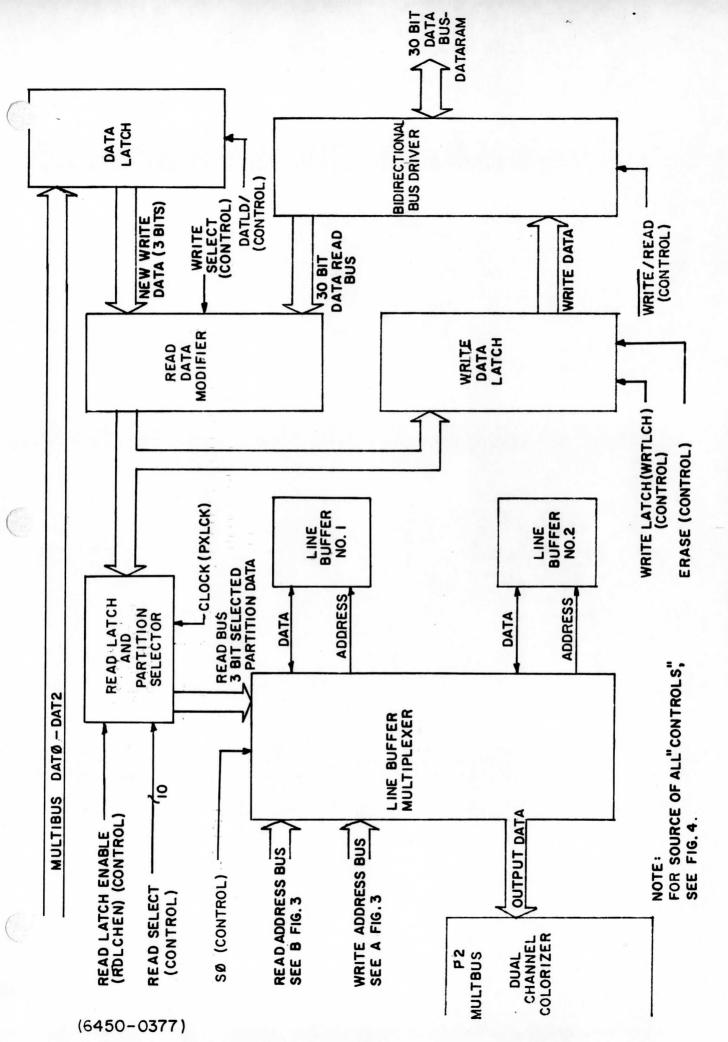

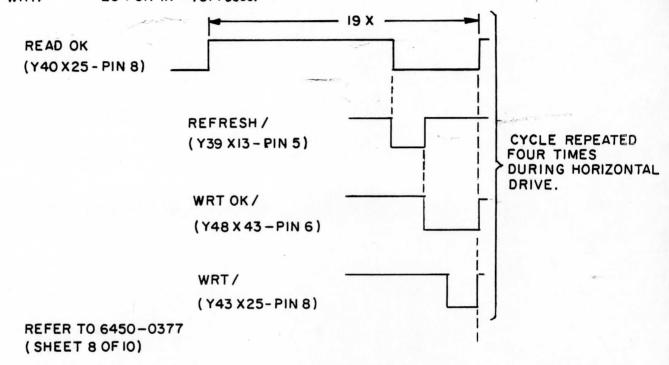

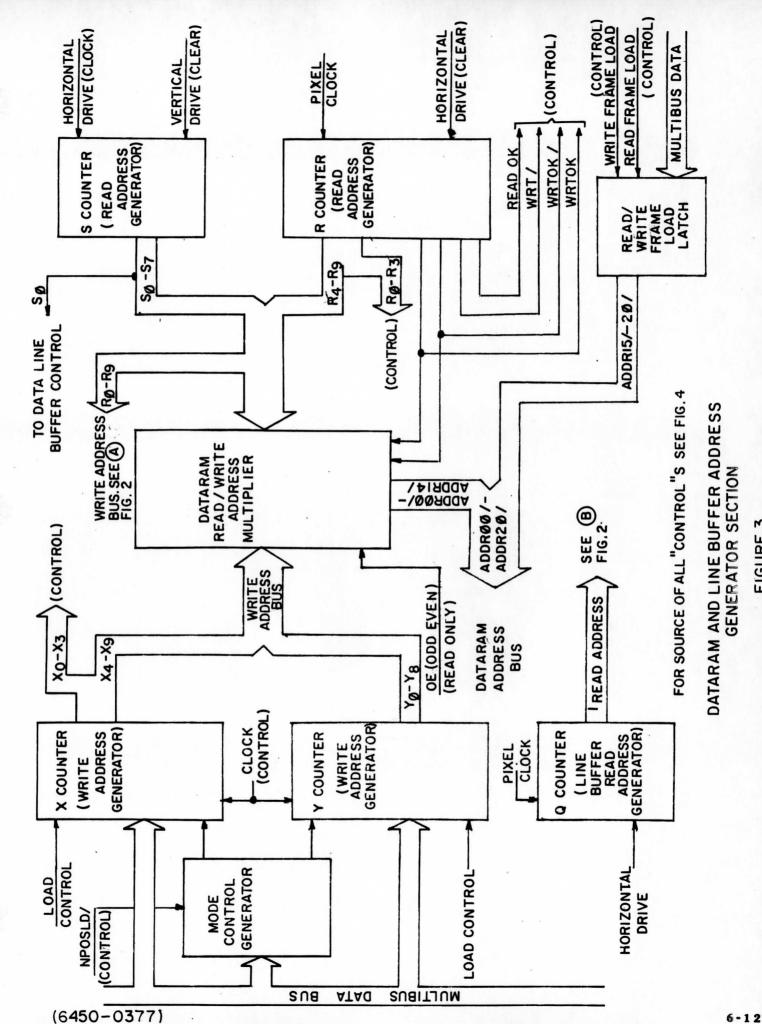

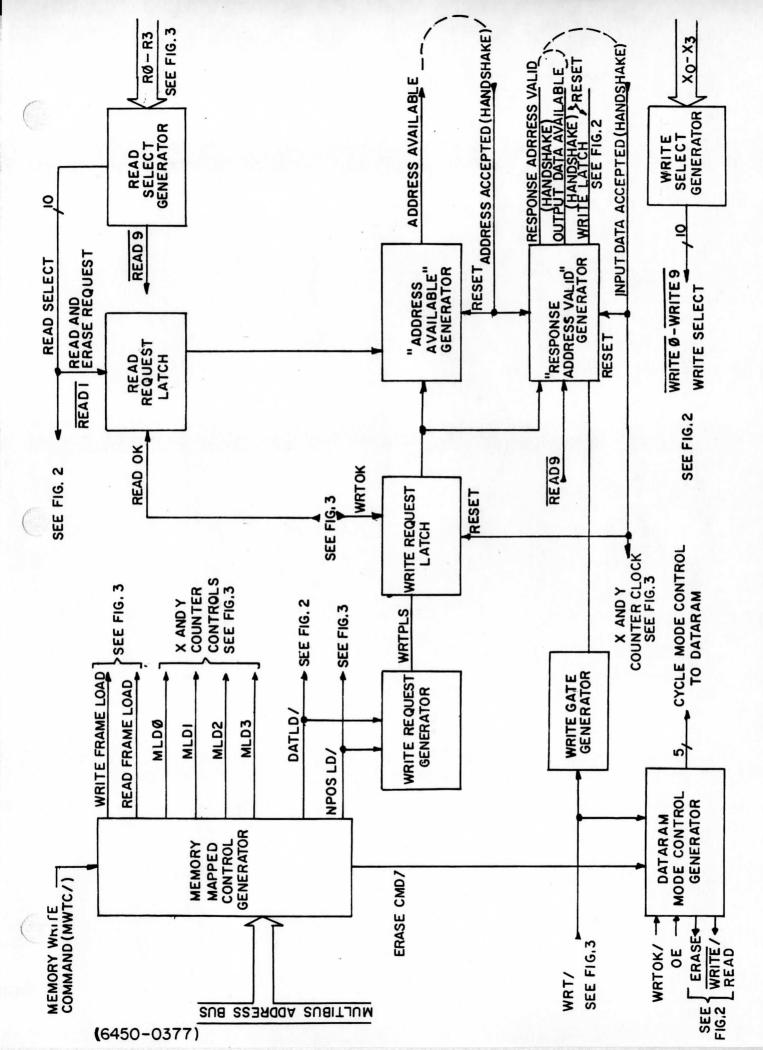

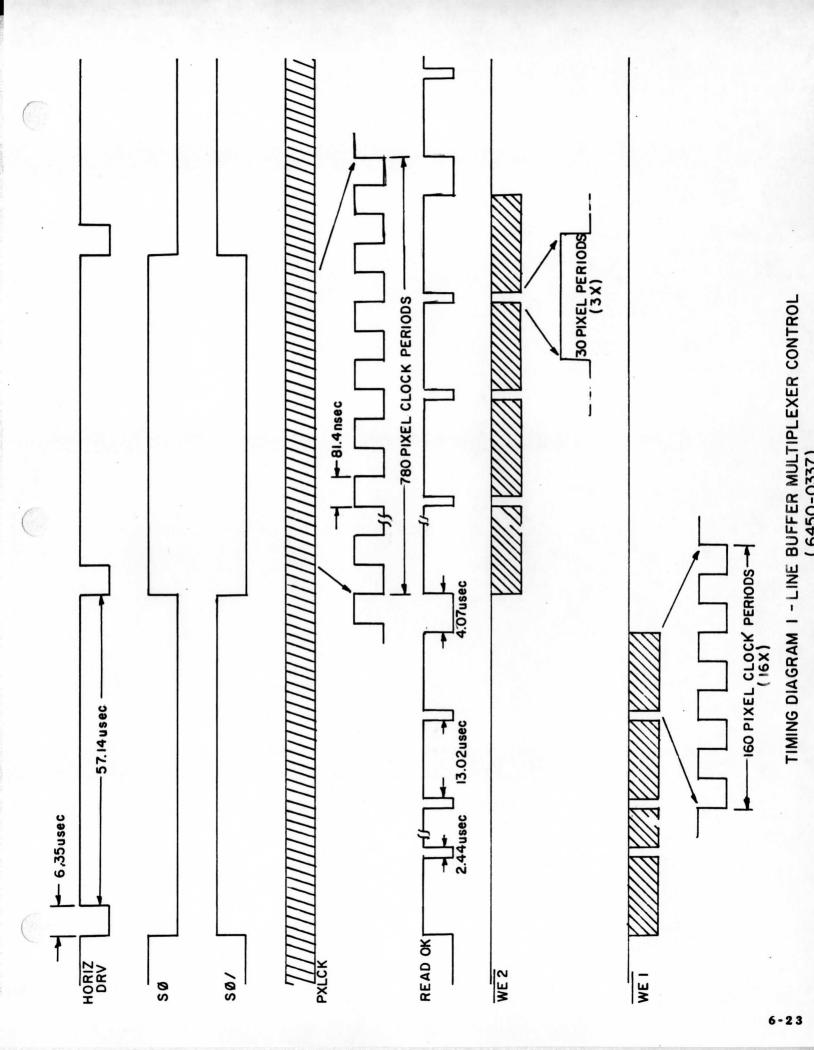

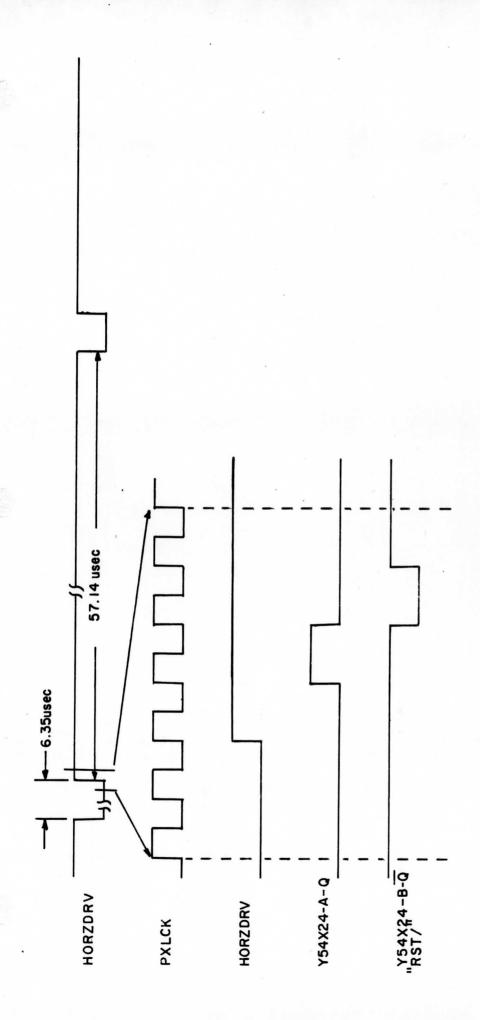

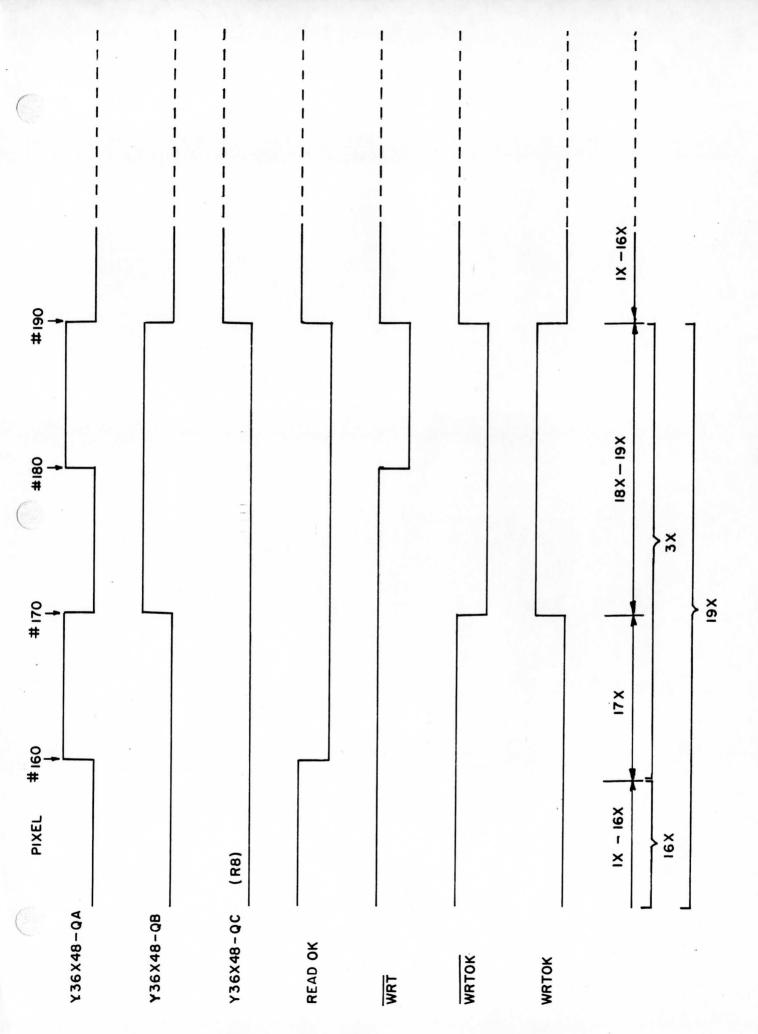

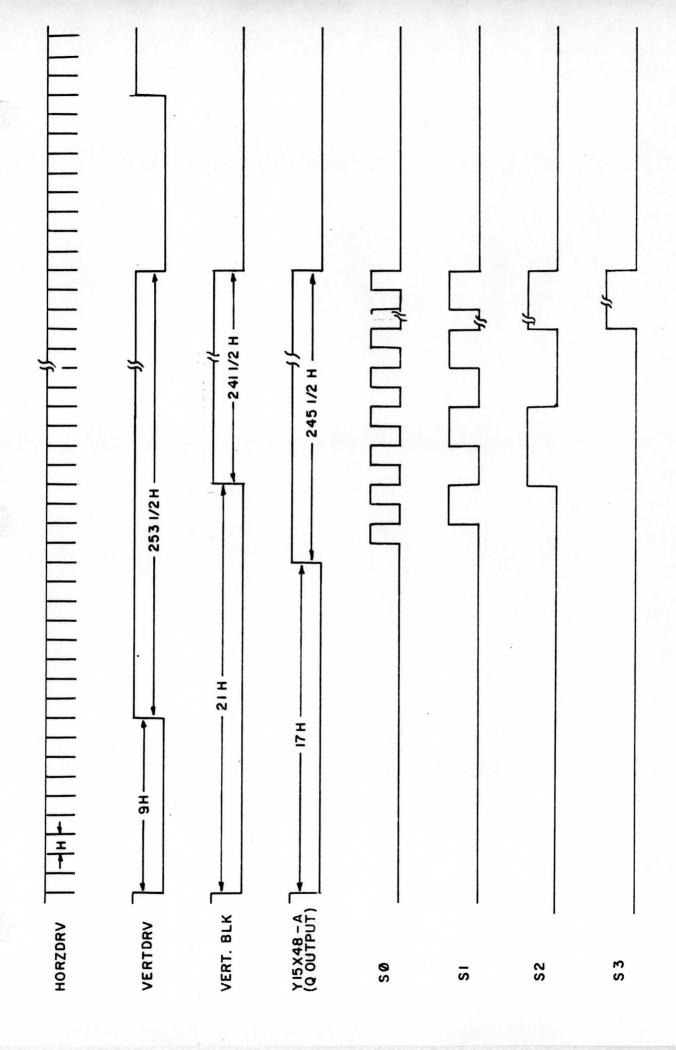

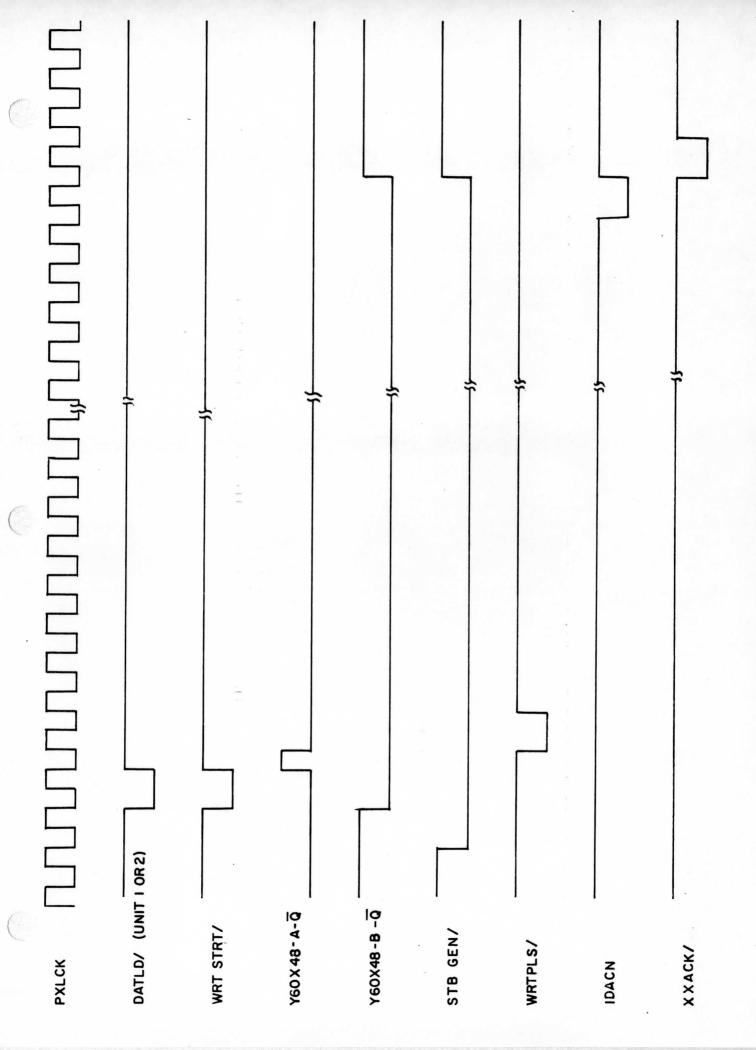

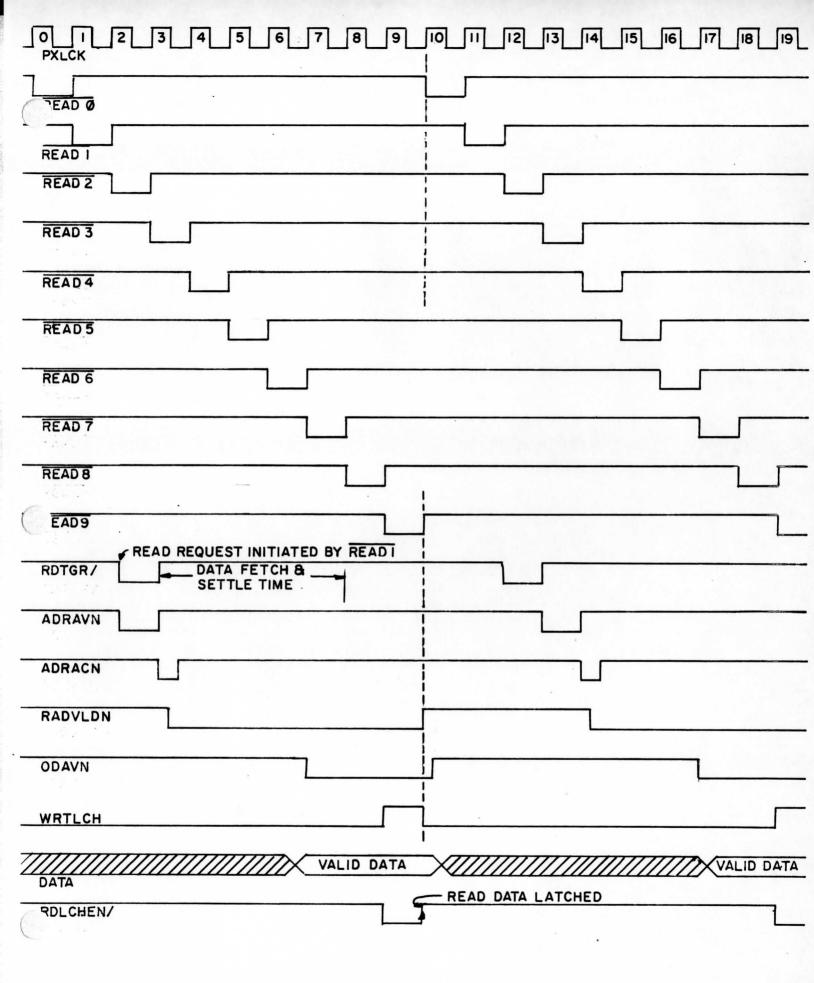

| SECTION 6: DATARAM CONTROL BOARD  Figure 1 - DATARAM Control Overview Block Diagram  Figure 2 - Data Formatting Section Block Diagram  Figure 3 - DATARAM and Line Buffer Address  Generator Section  Figure 4 - Control and Handshake Section Block Diagram  Timing Diagram 1 - Line Buffer Multiplexer Control  Timing Diagram 2 - R Counter Reset  Timing Diagram 3 - R Counter Cycle Reset  Timing Diagram 4 - S Counter  Timing Diagram 5 - Write Request Initiation  Timing Diagram 6 - Data Read Cycle | 6-8<br>6-12<br>6-15<br>6-28<br>6-30<br>6-32<br>6-41 |

| SECTION 7: DATARAM/MULTIBUS INTERFACE Figure 1 - DATARAM/Multibus Interface Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                     | 7-2                                                 |

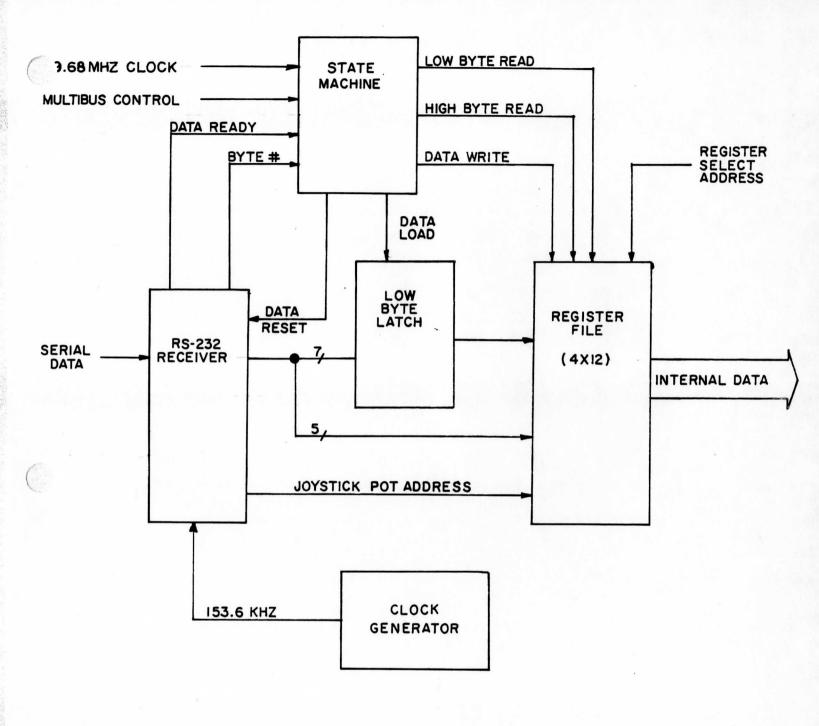

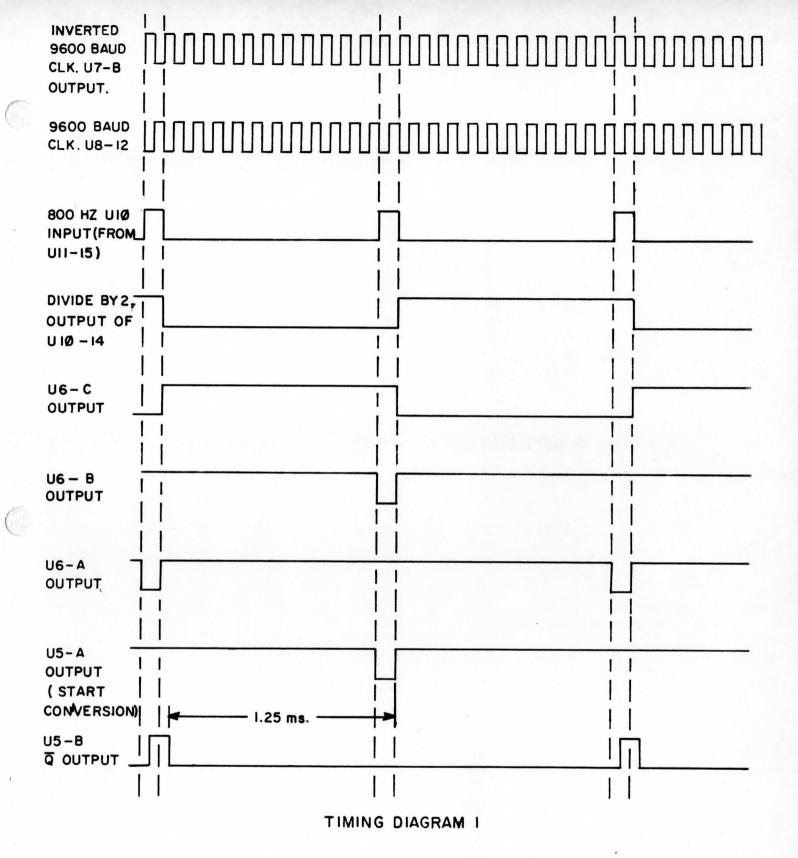

| SECTION 8: DIGITAL JOYSTICK BOARD  Figure 1 - Digital Joystick Board Block Diagram  Timing Diagram 1 - Digital Joystick Board                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

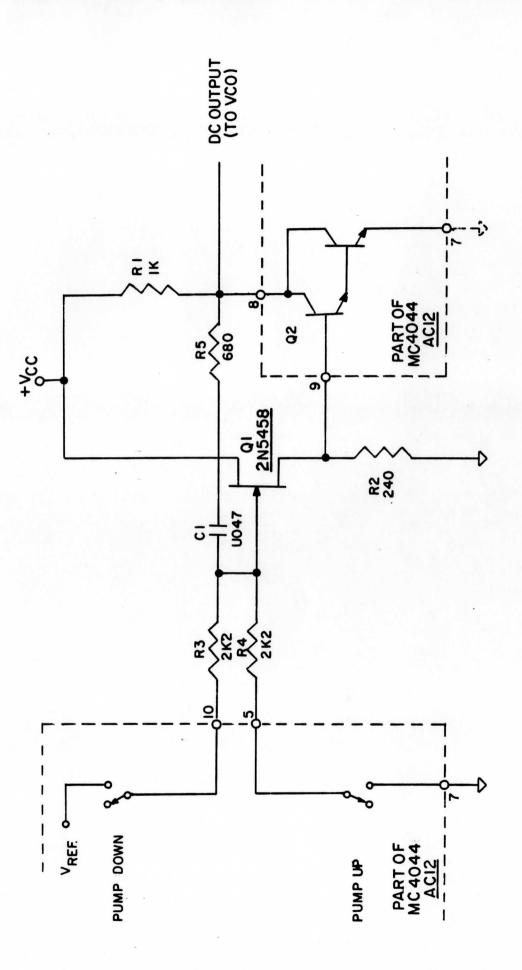

| SECTION 9: PAL/NTSC TV SYNC UNIT                  |      |

|---------------------------------------------------|------|

| Figure 1 - PAL/NTSC TV Sync Unit Block Diagram    | 9-2  |

| Figure 2 - Phase Comparator Filter Schematic      | 9-9  |

| Timing Diagram 1 - NTSC TV Divide-by-Seven Timing | 9-7  |

| Timing Diagram 2 - Reset Timing Generation        |      |

| SECTION 10: PAL/NTSC ENCODER BOARD                |      |

| Figure 1 - PAL/NTSC Encoder Board Block Diagram   | 10-2 |

(

( )

()

# SECTION 1 McIDAS WORKSTATION OVERVIEW TABLE OF CONTENTS

| INTRODUCTION                                                                                                                                                                                      | 1-1                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| East and West GOES Antennas. Archive/Playback IBM Computer (4381-2) Disk Storage Programmer Terminals Local Area Network Remote Communications Controller Conventional Data Input                 | 1-1<br>1-1<br>1-3<br>1-3<br>1-3<br>1-3<br>1-3<br>1-4<br>1-4 |

| Workstation Components IBM PC/AT. Enhanced Color Display (ECD) Keyboard. Mouse. BiT 3 MULTIBUS Adaptor Card. Color Monitor. NTSC/PAL Monitor. Printer                                             | 1-4<br>1-6<br>1-7<br>1-7<br>1-7<br>1-8<br>1-8<br>1-8<br>1-9 |

| Microprocessor  Cabinet/Chassis  Memory Storage System  12-Bit (Dual Channel) Colorizer-IDT RAM Version  60/50 Hz TV Timing and Colorizer-Brooktree  Cursor Generator  Host/Workstation Interface | 1-9<br>1-11<br>1-12<br>1-13<br>1-13<br>1-14                 |

### McIDAS PC/AT-BASED WORKSTATION OVERVIEW

### INTRODUCTION

The McIDAS PC/AT-based workstation is the link between the user and the McIDAS. It provides the animated display of satellite imagery and weather data. An IBM PC/AT computer allows the user to issue commands to the workstation and the host IBM mainframe, and receive alphanumeric information from the host. A large memory system stores image and graphics data; a color monitor is used to view this data, and a mouse or a pair of joysticks is used to position the cursor on the data display. Optionally, a printer is connected to the PC/AT to produce a hardcopy of the alphanumeric information.

A brief description of SSEC's version of the McIDAS is provided to describe how the workstation fits into the total system. Users' systems range from single McIDAS workstations, linked remotely to SSEC's McIDAS, to complete systems like the SSEC McIDAS, to more elaborate systems, similar to SSEC's McIDAS, but with more or different components. The McIDAS workstation description follows the McIDAS system description.

### McIDAS SYSTEM DESCRIPTION

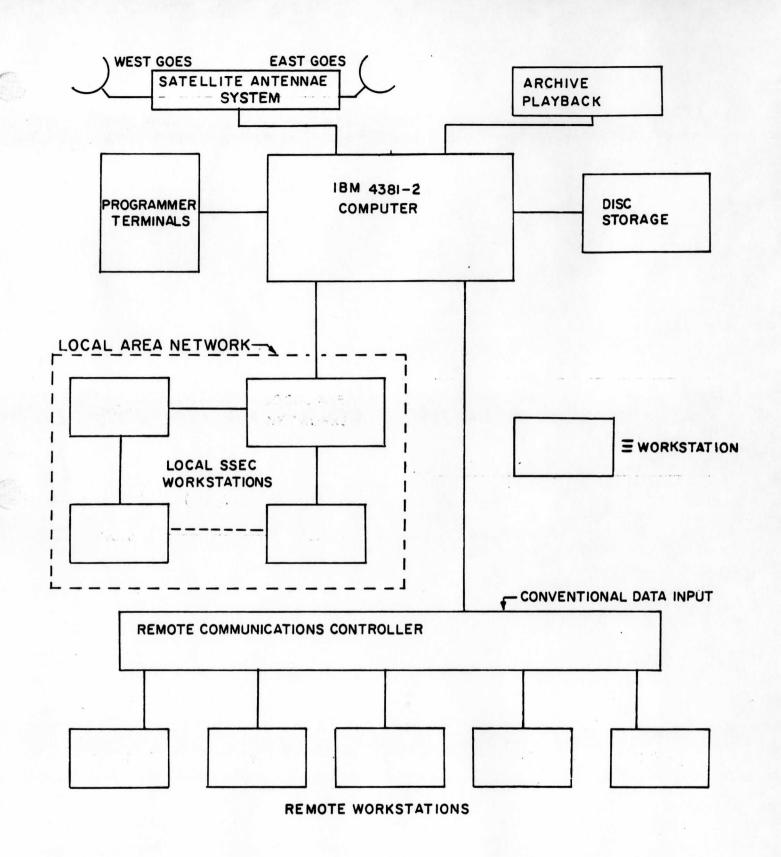

Figure 1 is a block diagram of the SSEC McIDAS. Each block or group of blocks is reviewed in terms of its function within the system.

### EAST AND WEST GOES ANTENNAS

The GOES (Geosynchronous Operational Environmental Satellite) antennas receive visible and infrared digitally-encoded images from the East and West GOES satellites.

### ARCHIVE/PLAYBACK

The raw GOES data are stored digitally on videocassette cartridges. The playback unit allows GOES raw data to be read into the system, at any time, for user analysis.

MCIDAS SYSTEM BLOCK DIAGRAM

FIGURE-1

### IBM COMPUTER (4381-2)

The IBM mainframe computer receives imagery data from the GOES antenna group or from archived tapes. The computer contains the operating system, application programs, and subroutines; it functions as a data processor, data base management system, and data analyzer.

### DISK STORAGE

Currently, the SSEC McIDAS has a storage capacity of approximately 12.8 gigabytes (12.8 billion bytes). The disk storage is divided into 6999 digital areas in which several data bases reside. The following are three of the major data bases:

- Image Files

- Meteorological Data (MD Files)

- Grid Files

An Image File (area) contains digitized satellite visual data or infrared sensor data.

A Meteorological Data File is a generic file for single-location observations (non-image), designed to accommodate many types of data under one generalized structure.

A Grid File contains fields analyzed at regularly-spaced latitude and longitude locations (grids) from observational data.

### PROGRAMMER TERMINALS

The programmer terminals are used for development of system software.

### LOCAL AREA NETWORK

The local area network (LAN) provides a high-speed (10 Mbits/sec) data link between McIDAS workstations and the IBM computer. McIDAS uses an "off-the-shelf" local area network system, called proNET manufactured by Proteon Inc., and an SSEC-fabricated IBM channel interface.

### REMOTE COMMUNICATIONS CONTROLLER

The Remote Communications Controller performs the same functions as the LAN but serves remote users. Workstations are usually connected to the Remote Communications Controller by dedicated telecommunication lines maintained by commercial firms such as AT&T. The data speeds (baud rates) are generally much lower (19.2K bits/sec or less) than those of the LAN. The terms "Local" and "Remote," as applied to workstations in Figure 1, refer to the data link type rather than geographical location. SSEC may have both local and remote workstations within a single room.

### CONVENTIONAL DATA INPUT

The McIDAS can ingest a wide variety of conventional weather data. This conventional data input is referred to as "point source" data and is used to maintain the Meteorological Data (MD) data base. Sources for conventional data include radiosondes, rocketsondes, ship reports, aircraft, and radar.

### McIDAS WORKSTATIONS

The McIDAS workstation is designed for animated display of satellite imagery and weather data. The following features are included in the workstation:

- real-time access to image and conventional data

- graphics overlays of images without image destruction

- animated displays of image or graphics frames at user-selectable looping rates of up to 15 frames/sec

- pseudocoloring of imagery

- user-selected graphics colors

- manual graphics drawing with joysticks or mouse

- satellite image combinations, forming three-dimensional, colorenhanced images

### McIDAS WORKSTATION DESCRIPTION

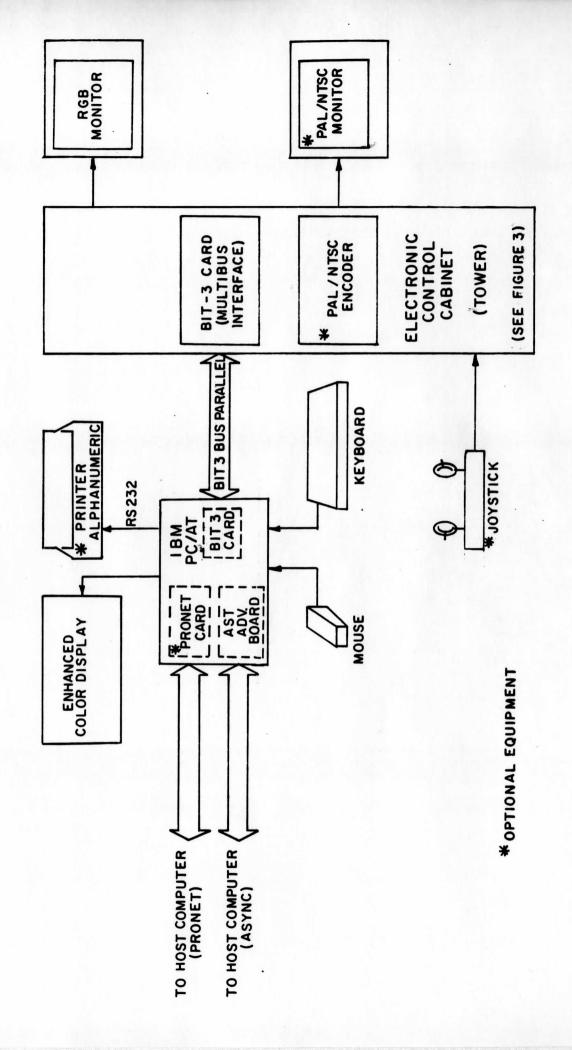

The Figure 2 block diagram shows the components that constitute a complete workstation. Blocks containing an asterisk (\*) may be omitted in some workstations, with a corresponding reduction in workstation capability and flexibility.

MCIDAS-PC/AT WORKSTATION BLOCK DIAGRAM FIGURE-2

### WORKSTATION COMPONENTS

The blocks (components) in Figure 2 are individually addressed according to their functions within the workstation. Some components are standard "off-the-shelf" items and may be substituted with components of similar specifications. When these components are described, component specifications are included, because make and model descriptions are more likely to change frequently.

### IBM PC/AT (6- AND 8-Mhz VERSIONS)

The McIDAS workstation evolved over a period of many years. Until recently, the workstation was interfaced directly to the host computer. In this configuration, all computations and meteorological analysis is performed by the host computer, and all user interaction is performed via a CRT terminal.

The IBM PC/AT computer was integrated into the workstation to reduce the host's workload, by performing some of the workstation-related tasks at the workstation. The PC/AT integration process is an evolutionary development process.

The IBM PC/AT equipment group consists of:

- IBM PC/AT computer

- Enhanced Color Display (ECD)

- Keyboard

- Mouse

- BiT-3 MULTIBUS Adapter

### IBM PC/AT Computer

Currently, the PC/AT is used in two workstation configurations, a stand-alone configuration, and a full-function configuration. In either configuration, the PC/AT integrates the keyboard, the Enhanced Color Display (ECD), and the mouse into a user interaction terminal.

The PC/AT communicates with the host computer and, in the full-function configuration, with the Electronic Control Cabinet (Tower). Also, the PC/AT reformats data intended for the Tower (full-function configuration) to a Bisync protocol.

The stand-alone PC/AT workstation uses its ECD to display satellite images, graphics, image cursor, and alphanumeric data. To operate in this mode, the PC/AT requires additional memory and an Enhanced Graphics

Adapter (EGA). This type of workstation is frequently referred to as an "EGA-style" workstation. The EGA is required for increased image resolution beyond the IBM Color Graphics Adaptor display resolution. The image resolution is still much less than the full-function workstation. Also, the EGA-style workstation can store a total of 16 image/graphics frames while the full-function system can store up to 128 images, plus a maximum of 64 graphics frames. However, the EGA-style workstation has no image enhancement or combinational abilities. Finally, the EGA-style workstation relies entirely on the mouse for image cursor control. This arrangement is satisfactory for most cursor requirements.

The full-function PC/AT workstation contains the Electronic Control Cabinet (Tower). The Tower provides mass storage for image and graphics storage, color and monochrome monitor interfaces, cursor generation and control, and a monochrome interface.

The IBM PC/AT computer hardware is documented by the manufacturer. Refer to Appendix A for applicable manuals.

### Enhanced Color Display (ECD)

The ECD is driven by the PC/AT computer, and can function as an image/graphics monitor as well as an alphanumeric display, when the PC/AT functions as an EGA-style workstation. When the PC/AT is connected to the tower (full-function), the ECD is primarily used to display alphanumeric data. The ECD is documented by the manufacturer (IBM). Refer to Appendix A for additional references.

### Keyboard

The keyboard provides the user interaction with the McIDAS. It is a standard keyboard supplied with the IBM PC/AT. The keyboard is documented by the manufacturer. Refer to Appendix A for additional reference information.

### Mouse

The mouse provides the PC/AT with cursor control. The mouse performs the same functions as a single joystick in the full-function workstation. Because certain wind measurement processes (WINDCO) require two cursors, controlled by two joysticks, the mouse cannot emulate all cursor functions at this time. The mouse is also used during alphanumeric menu displays for cursor (flashing underline symbol) position.

### BiT 3 MULTIBUS Adaptor Card

The full-function workstation consists of the IBM PC/AT equipment group, interfaced to a Tower. Subassemblies and PC cards within the Tower are interconnected by the industry-standard MULTIBUS TM (MULTIBUS is a registered trademark of INTEL Corporation). The IBM PC/AT requires an adapter to make it compatible with the MULTIBUS.

BiT 3 Computer Corporation manufactures a two-card adaptor set which interfaces the PC/AT to the MULTIBUS. One card plugs into the PC/AT, while the other plugs into the MULTIBUS. The two cards are interconnected by two 50-conductor flat cables. The MULTIBUS Adaptor cards are documented by BiT 3. Refer to Appendix A for references.

### COLOR MONITOR (RGB)

The CONRAC 7211 is a standard RGB (red, green, blue) color monitor, used to display color and monochrome images and graphics. The inputs to the monitor are red, green, and blue drive signals and composite sync signals from the electronic control cabinet. The monitor is driven to a resolution of 640 visible picture elements (pixels) by approximately 480 visible scan lines. The CONRAC 7211 is commercial equipment, documented by the manufacturer. Any high-resolution RGB monitor can be substituted for the CONRAC 7211.

### NTSC/PAL MONITOR

The full-feature workstation (Tower) contains a PAL (Phase Alternating Line) encoder or an NTSC (National Television Standards Committee) encoder. An NTSC or PAL monitor can be used to display the composite video output of this encoder. The monitor is not essential for workstation operation and therefore may be eliminated.

### PRINTER

The printer produces hardcopy maps, tables, or listings. The printer is not essential for workstation operation and therefore may be eliminated. The printer is interfaced to the workstation via an RS-232 port in the IBM PC/AT, typically at a baud rate of 4800 bits per second. Currently, an OKIDATA Microline 293 printer is used. The OKIDATA Microline 293 is a standard commercial printer, documented by the manufacturer.

### JOYSTICKS

The Joystick module positions the cursor on the monitor. The module consists of two joysticks, containing two potentiometers and an electronics board. The potentiometers supply analog position information to the electronics board. The electronics board transforms the analog input data to digital data and serially transmits this data to the Electronic Control Cabinet. Typically, the right joystick provides coarse position control while the left provides vernier (fine) control. The data is transmitted as 8-bit ASCII, with two stop bits, parity, and one start bit. The parity bit is always transmitted as a logic "one". The electronic mouse can perform most joystick functions; thus, the joysticks are optional in some applications.

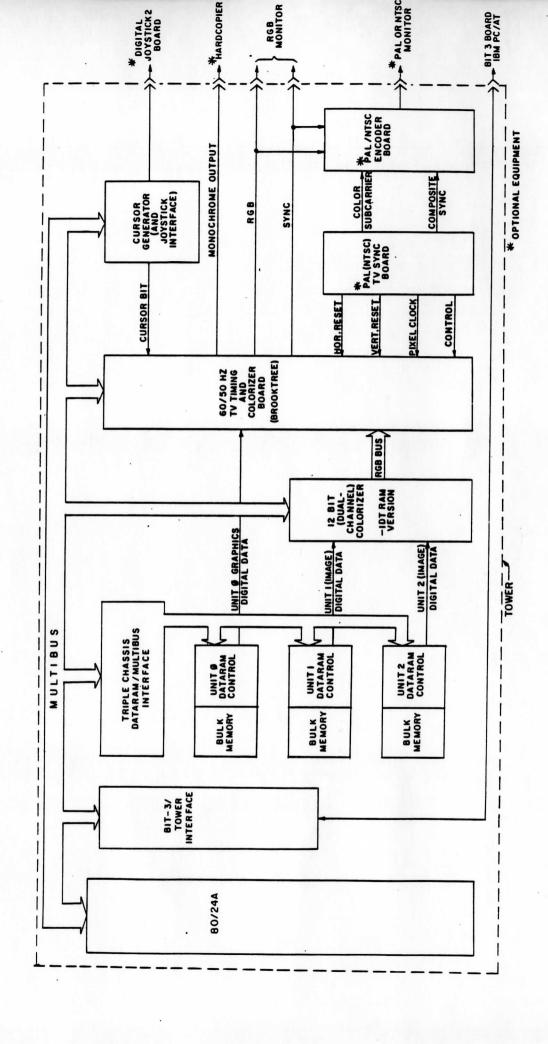

### ELECTRONIC CONTROL CABINET (TOWER) OVERVIEW

Figure 3 is a block diagram of the workstation, showing the Electronic board, Control Cabinet, and external components. Except for the DATARAM memory storage, the BiT 3, and the Intel 80/24A microprocessor board, all control cabinet blocks are designed and built by SSEC. The Electronic Control Cabinet is a standard 19-inch rack, often referred to as "the Tower."

### MICROPROCESSOR

The microprocessor controls the data flow between the various boards and components in the workstation. It also controls communications between the IBM PC/AT and the Electronic Control Cabinet. The microprocessor accepts commands or data "packets" from the PC/AT, decodes the command or destination-device-address, and executes the command or data transfer.

The microprocessor is an Intel iSBC 80/24A single-board computer, having 8K bytes of on-board RAM. The board supports a maximum of 32K bytes of EPROM (Erasable Programmable Read Only Memory). Three of the available four EPROM chips contain the microprocessor's instructions, constants, and most tables. The fourth EPROM chip contains only a video image compression table. (Refer to the 12-Bit (Dual Channel) Colorizer-IDT RAM Version overview.) The board supports one serial I/O (Input/Output) device via the J3 jack. The J3 jack is connected to the CRT terminal during diagnostic testing. The 80/24 board uses an Intel 8085A 8-bit

FUNCTIONAL BLOCK DIAGRAM

ELECTRONIC CONTROL CABINET (TOWER)

FIGURE-3

microprocessor for the central processor unit; it performs on-board processing as well as on- and off-board control.

### CABINET/CHASSIS

The Electronic Control Cabinet (Tower) is a standard 19-inch electronics rack. The rack has an overall height of 56 inches, including the casters. The cabinet has an overall depth of 30 inches and width of 24 inches. The rack has a front opening of 44 inches by 19 inches and houses the following five 19-inch modular electronic units:

- PAL/NTSC Encoder (optional)

- MULTIBUS chassis

- DATARAM memory storage (units ∅, 1, and 2)

Each module contains its own DC power supply which plugs into a switched convenience AC outlet panel, located near the bottom rear of the cabinet.

The PAL/NTSC Encoder is located at the top of the cabinet (when installed) and enables the workstation to produce NTSC or PAL composite color video. The composite color video can be used to drive an optional NTSC or PAL Color Monitor and modulate a commercial TV transmitter. The PAL/NTSC Encoder is designed and manufactured by SSEC and is documented in Section 10 of this manual.

The MULTIBUS chassis was designed and is fabricated by SSEC. Boards are accessed through the front of these SSEC enclosures. The MULTIBUS chassis contains its own DC power supplies and a card cage that accepts up to nine PC cards.

All boards within the card cage are interconnected by the card cage backplane, through a bus structure called MULTIBUS<sup>R</sup>. MULTIBUS is registered trademark of Intel Corporation and has become an industry standard. The standard is now controlled by IEEE (IEEE 796). The P1-bus consists of 16 address lines, 8 data lines, control lines, interrupt lines, and bus exchange lines.

All SSEC boards, housed in the card cage, are designed to be MULTIBUS-compatible with the Pl connector. SSEC uses the P2 connector for various McIDAS-specific timing and video signals.

The DATARAM memory storage units are located below the MULTIBUS chassis. A DATARAM control board, built by SSEC, is located in each of the memory storage units. The DATARAM control board connects the MULTIBUS to the memory storage system via the Triple Chassis DATARAM/MULTIBUS

Interface. Additional information on the Memory Storage Unit is found in the next section of the Overview (Memory Storage System).

### MEMORY STORAGE SYSTEM

The Memory Storage System consists of three separate memory storage units. One unit stores graphics overlay data while the other two units store compressed image data. Each unit can be populated with from one to four storage array boards. Each array board provides storage for 16 frames of video data. Increasing with the number of array boards, the memory storage unit can store 16, 32, 48, or 64 graphics frames and 32, 64, 96, or 128 image frames.

In response to the significant amount of memory required for video storage, SSEC developed a memory control board that allows the microprocessor to store images and graphics in the Memory Storage Units. These data are automatically retrieved when the microprocessor addresses the unit via a frame number for read operations. Video data is stored one pixel at a time by addressing the frame number, video line number ( $\emptyset$ -511), and pixel position within that line ( $\emptyset$ -639). Video data is read sequentially beginning with the starting address and ending with the last pixel address of the frame. The read process is repeated until the user selects a different frame number. During the read process, data is read sequentially by the Control board and output to the 12-Bit (Dual Channel) Colorizer-IDT RAM Version board (image data) or the 6 $\emptyset$ /5 $\emptyset$  Hz TV Timing and Colorizer-Brooktree (graphics) board, at TV pixel painting rates. See the manufacturer's literature for more information on the memory storage modules.

### 12-BIT (DUAL CHANNEL) COLORIZER-IDT RAM VERSION

The 12-Bit (Dual Channel) Colorizer-IDT RAM Version board expands (decompresses) the two 3-bit video image channels into two 6-bit channels. The 6-bit channels are used as address inputs to an enhancement table. The table is user-programmable via the host computer. The 15 binary output bits from the table are divided into three 5-bit buses which represent magnitudes of red, green, and blue (RGB) drive signals. The table provides a means to assign color drive intensities (pseudocolors) as a function of the 6-bit image channel inputs, individually or in combination with each other.

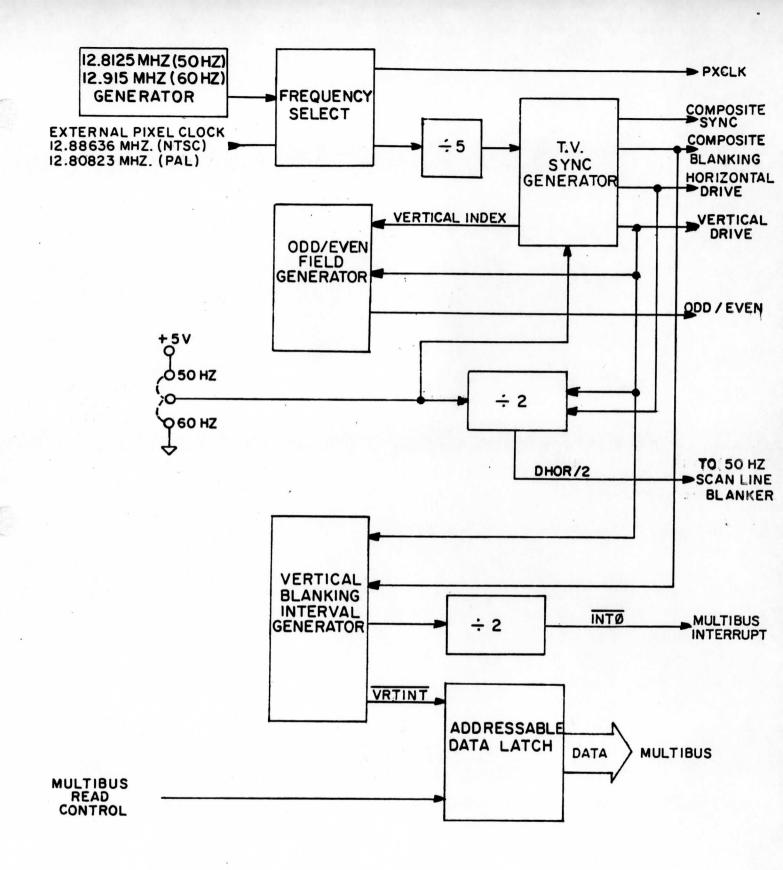

### 60/50 HZ TV TIMING AND COLORIZER-BROOKTREE

The RGB bus signal outputs from the 12-Bit (Dual Channel) Colorizer-IDT RAM Version board are inputs to the 60/50 Hz TV Timing and Colorizer-Brooktree board. The 3-bit graphics bus and the cursor bit are also inputs to this board. This board does the following:

- generates all TV timing signals

- multiplexes image, graphics, and cursor data

- converts the digital video into analog video, suitable for driving a standard RGB monitor

- assigns color to the graphics and cursor data

The TV timing signals are horizontal and vertical drive signals, used by frame-processing logic; PXLCK (pixel clock), used for timing and synchronization of all digital video signals; and composite sync, used by the RGB monitor.

Each pixel, as seen on the RGB monitor screen, is either an image pixel, a graphics pixel, or a cursor pixel. The TV Timing and Colorizer board assigns priority to the pixel type, from highest to lowest, as follows:

- cursor

- graphics

- image

Graphics bits are processed by a color enhancement table, similar to the process by which image color enhancement is performed on the 12-Bit (Dual Channel) Colorizer-IDT RAM Version board. For each cursor bit value ("Ø" or "1"), eight colors can be loaded into the table; the 15 RGB outputs of the lookup table result in 32,768 user-selectable colors and brightness levels.

The digital RGB video data is applied to the digital-to-analog (D-to-A) converters, combined with composite sync and output to the RGB monitor. The TV Timing and Colorizer board also provides a monochrome output to drive hard copiers.

### CURSOR GENERATOR

The Cursor Generator combines two unrelated functions. This board generates the cursor symbol, and interfaces the serial input joystick data to the microprocessor.

When the user positions the joysticks, the joystick board generates a serial output data stream containing cursor position information. The Joystick Interface section of this board converts the serial data stream to parallel data; parallel data is transmitted via the MULTIBUS to the microprocessor.

The microprocessor updates its stored cursor position registers and transmits the updated values back to the Cursor Generator portion of the board. The microprocessor also transmits cursor symbol size and shape information. The Cursor Generator uses these input parameters and TV timing signals to determine if the pixel (on the RGB monitor) about to be painted is a cursor pixel. If the pixel is a cursor pixel, a cursor bit is sent to the 60/50 Hz TV Timing and Colorizer-Brooktree board.

### HOST/WORKSTATION INTERFACE

Early versions of the McIDAS workstation communicated directly with the host via Bisync, a subset of the IBM Bisync communications protocol. Bisync transfers data from a data source to a data receiver in the form of message packets. SSEC designed and uses a protocol which is embedded into the data portion of the Bisync protocol. This protocol (referred to hereafter as the "workstation protocol") is documented in the MIDDS Host to Terminal - Terminal to Host System Protocol Description, dated 26 June 1985 by SSEC (Rev. Level 1). The communications protocol is half duplex, byte oriented, and binary synchronous. Host software and workstation hardware and firmware evolved using this communications scheme. Backward compatibility of new communications schemes and workstation design were maintained to allow owners of older systems to update their systems.

Later in the workstation development history, a local area network (LAN) system was developed to connect several workstations within a limited physical area to a host computer. The system is designed around a proprietary LAN designed and fabricated by Proteon Inc. The LAN is known as proNET , and features a data throughput rate of 10Mbits per second. A drawback of the system was that the LAN reformatted the Bisync message packets by embedding the Bisync protocol in the proNET protocol, impeding the desired backward compatibility. A solution to this problem was to sandwich the proNET LAN between two SSEC-designed and -fabricated message protocol adapter cards. This arrangement allows the host software

and the workstation hardware and firmware to remain virtually unchanged when the McIDAS is interconnected via the LAN. Thus, the workstations and host perform as if they are connected via a Bisync link.

The latest generation of the McIDAS workstation contains a PC/AT computer. Because of its diverse communications capability, the PC/AT is functionally located in the communications path between the Tower and the host. Protocol conversion by the PC/AT is an advantage of performing all host to workstation-workstation to host communications via the PC/AT. Thus, the Tower communications firmware and hardware can remain virtually unchanged, if the PC/AT communicates with the Tower, through the Bisync protocol.

The PC/AT does not have Bisync capability, and its internal bus structure is incompatible with MULTIBUS. The following paragraphs describe the solutions to these problems.

A bus-to-bus converter called a Multibus Adapter, designed and manufactured by BiT 3 Computer Corporation, solves the PC/AT bus-to-MULTIBUS incompatibility problem. The MULTIBUS Adapter consists of two boards. One board plugs into the PC/AT while the other plugs into the Tower. The two boards are connected by two 50-conductor ribbon cables. The MULTIBUS adapter contains a bi-ported RAM which resides in the MULTIBUS and PC/AT address domains. The bi-ported RAM serves as a two-section message packet buffer. One section of the buffer functions as a transmit buffer; the other section functions as a receive buffer.

The Tower interrupts the PC/AT to inform it when it will accept message packets. The Tower produces these interrupts at a 30hz rate; they occur on alternate vertical retrace intervals. The message packets, transmitted to the Tower from the PC/AT, have the same message packet format as that formerly transmitted from the host to the workstation (Bisync).

The Bisync communications scheme was replaced by Async for greater data transmission efficiency and compatibility with the PC/AT. The Async and Bisync protocols are different. The Bisync protocol (also known as  $\emptyset 2, \emptyset 3$ ) contains embedded framing characters, begins with an ASCII  $\emptyset 2$  (STX-Start of Text), and ends with an ASCII  $\emptyset 3$  (ETX-End of Text). The  $\emptyset 2, \emptyset 3$  protocol gets its name from the STX and ETX codes. The Async protocol begins each message packet with FØH, and is sometimes referred to as the "FØ protocol." Each async message packet contains a message-type

identification code. One of the message types is an  $\emptyset2,\emptyset3$  protocol. Thus, the FØ protocol can embed an  $\emptyset2,\emptyset3$  type message.

Because the protocols are different, the host communicates with the workstation via a protocol converter, allowing host software to remain  $\emptyset 2, \emptyset 3$  protocol oriented.

The protocol converter is connected to the PC/AT via a pair of high-speed, error-correcting modems, such as Fastlink modems. These modems feature several carriers and automatically adjust baud rates and select the most error free carriers to maintain reliable communications at the highest baud rates. The modems allow communications over commercial telephone lines and/or dedicated lines at baud rates of up to 19.2K bits per second. These modems are self-pacing, using X-on/X-off to start and stop data transmissions respectively.

There are two conditions under which message packets are generated by the PC/AT. First, "workstation protocol" messages are transmitted from the host to the PC/AT by embedding the "workstation protocol" into the Async protocol. The PC/AT extracts the workstation protocol from the Async message, embeds it into a Bisync formatted message, and forwards the packet to the Tower. Second, the PC/AT interprets single-character user's commands entered at its keyboard and forms Bisync formatted packets. These packets are transmitted to the workstation where they are executed by the Tower. These messages contain image and graphics frame control, and cursor control.

Several messages are transmitted from the Tower to the PC/AT, but only the following are processed:

- ID response the response contains the Tower's ID, maximum number of image frames, and maximum number of graphics frames. The PC/AT ignores the ID, but retains the remaining data.

- raw joystick data the Tower sends joystick position data.

- Tower cursor state the Tower sends cursor size and position data to the PC/AT.

Proteon Inc. designed and fabricated a proNET adapter board which is optionally installed in PC/AT workstations that use proNET. The PC/AT converts incoming proNET formatted messages to Bisync format and forwards them to the Tower via the MULTIBUS adapter. For messages from the PC/AT or Tower to the host, the PC/AT converts the messages to proNET-compatible format.

The BiT 3 MULTIBUS Adapter interfaces the MULTIBUS to the PC/AT; the memory addresses and I/O ports residing on the MULTIBUS can be accessed by the PC/AT. However, at present, all MULTIBUS I/O port accesses are made only by the 80/24A card. The <u>capability</u> of the PC/AT to address the MULTIBUS I/O ports is a design feature that allows expansion of the PC/AT's role in the McIDAS workstation. The following paragraph describes the integration of this feature.

The PC/AT addresses I/O ports with a 3-digit hexidecimal (hex) addresses (Ø-7FFH). Any block of I/O addresses, not used internally by the PC/AT or any of its optional adapter cards, can be assigned as MULTIBUS I/O ports, via programming on the MULTIBUS Adapter board. The 8Ø85 microprocessor on the 8Ø/24A microcomputer card addresses I/O ports using a 2-digit hex address. Furthermore, the 8Ø85 writes the port address to both the upper eight bits and the lower eight bits of the MULTIBUS. This allows the MULTIBUS board designer the option of decoding specific I/O port addresses using the upper, lower, or combinations of the upper and lower eight bits of the MULTIBUS address bus. Because of the 8Ø85's port addressing scheme, PC/AT port addresses may appear at first glance to have little relativity to the 8Ø/24A's port addresses. Table 2 shows the port address correspondence and the portion of the MULTIBUS that is used by the specific board for the port address decode.

| 8Ø85 port | PC/AT port | Board              | Decode                               |

|-----------|------------|--------------------|--------------------------------------|

| вØн       | в328Н      | Dual Channel Col.  | Upper four bits and lower three bits |

| B1H       | B329H      | Dual Channel Col.  | "                                    |

| в2н       | B32AH      | Dual Channel Col.  | "                                    |

| взн       | B32BH      | Dual Channel Col.  | <b>"</b>                             |

| 73H       | 7328H      | TV Timing and Col. | Upper eight bits                     |

| 83H       | 8328H      | TV Timing and Col. | "                                    |

| 93H       | 9328H      | TV Timing and Col. | "                                    |

| 38H       | Ø338H      | Cursor/Joy         | Lower eight bits                     |

| 39H       | Ø339Н      | Cursor/Joy         | "                                    |

| 3AH       | Ø33AH      | Cursor/Joy         | "                                    |

| 3BH       | Ø33BH      | Cursor/Joy         | "                                    |

| 3CH       | Ø33CH      | Cursor/Joy         | "                                    |

| 3DH       | Ø33DH      | Cursor/Joy         | "                                    |

| 3EH       | Ø33EH      | Cursor/Joy         | "                                    |

| 3FH       | Ø33FH      | Cursor/Joy         | "                                    |

Table 2

In addition to the PC/AT port addresses shown in Table 2, the PC/AT uses port addresses Ø3ØØH-Ø3Ø7H for the proNET Adapter card. Finally, the BiT 3 MULTIBUS Adapter card requires several I/O port addresses for board control. These ports are available to both the MULTIBUS and the PC/AT. The MULTIBUS port addresses 7CH-7FH correspond to PC/AT port addresses Ø32ØH-Ø323H, and are used for BiT 3 MULTIBUS Adapter board control.

Regardless of interface type (proNET or Async), bisync protocol data is transferred between the PC/AT and the Tower. The PC/AT performs required protocol conversion on the workstation end of the communications interface. Host-to-workstation message transmissions consist primarily of:

- ASCII text to the ECD

- ASCII text to the printer

- graphics plotting parameters (starting points, line lengths and directions)

- pseudocoloring table loading data

- TV image data

- cursor size, shape, and position

- image looping parameters

- graphics and cursor color palette loading data

- workstation ID number

- TV frame numbers

Workstation-to-host message transmissions consist primarily of:

- keystroke characters

- workstation ID, including number of image and graphics frames available (generally ignored by the IBM host)

- TV image and graphics display status—frame number shown and upper and lower loop bounds

- raw joystick position data

### WORKSTATION SUMMARY

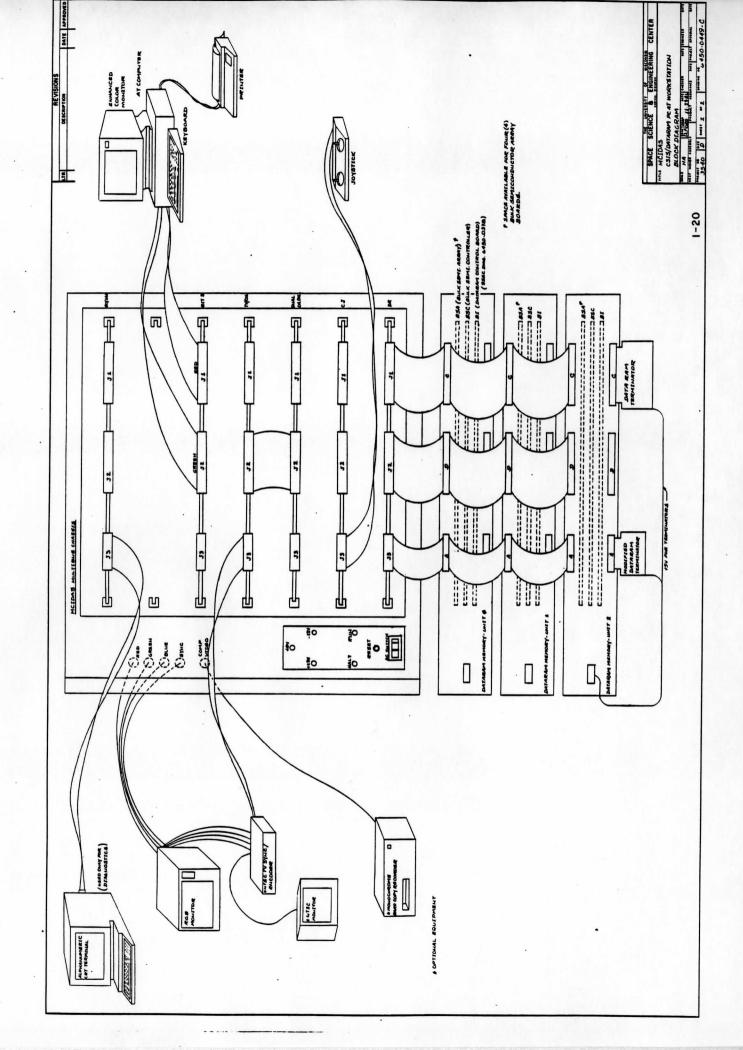

The workstation is best summarized by tracing a user's command through the system. For this example, assume the user wants to transfer an image frame to the workstation. Refer to Figure 4. The user types the proper sequence of characters at the PC/AT's keyboard to request the desired image from the host. (The input data format is located in the

McIDAS Applications Guide.) The PC/AT formats the command into a message packet and transfers the packet to the Host. The host deciphers the received packet, determines that the workstation has requested an image frame, and transmits the image, line by line.

The host forms each image line into a 642-byte packet, consisting of a two-byte image line number and 640 six-bit pixel data values. transmits the packets to the workstation's PC/AT. The PC/AT forwards the packet to the Tower. The microprocessor strips the "image line number" from the message packet and transfers this data to the appropriate Memory Storage Unit's DATARAM control board. The DATARAM control board loads the image line number into the pixel address generation section of the DATARAM control board. Now, the microprocessor processes each of the 640 six-bit pixel data values in a compression algorithm. The algorithm reduces the 6-bit pixel data to 3-bit pixel data, thereby reducing the memory storage requirements by 50 percent. After each pixel is processed, it is transferred to the DATARAM control board, which loads the pixel into memory and increments the pixel address counter. This process continues until each of the 640 pixels have been processed and stored. For each image frame, a total of about 490 packets (as described above) are transferred from the host and processed and stored by the workstation.

4/PCAT/01

## SECTION 2 SINGLE BOARD COMPUTER TABLE OF CONTENTS

| INTRODUCTION                    | 2-1 |

|---------------------------------|-----|

| HARDWARE FUNCTIONAL DESCRIPTION |     |

| Microprocessor                  |     |

| Memory and I/O Mapping          |     |

| EPROM                           | 2-5 |

| RAM                             | 2-5 |

| Serial I/O Interface            |     |

| General Purpose Timer           | 2-5 |

| Parallel I/O Interface          |     |

| Interrupt Controller            |     |

### SINGLE BOARD COMPUTER

### INTRODUCTION

The Single Board Computer consists of an Intel<sup>R</sup> iSBC 80/24A<sup>TM</sup> single board microcomputer. This document provides only a functional overview of the Single Board Computer. For complete hardware documentation of the iSBC 80/24A<sup>TM</sup>, see Intel<sup>R</sup>'s <u>iSBC<sup>R</sup> 80/24A SINGLE BOARD COMPUTER HARDWARE REFERENCE MANUAL</u> (Manual order number 148437-001). Note: Intel, iSBC, and MULTIBUS are registered trademarks of Intel Corporation.

For a more complete understanding of the McIDAS workstation and system, it is necessary to understand the workstation/host interface protocol, the workstation operational firmware and the diagnostic firmware. The workstation/host interface protocol is described in the SSEC document, HOST TO TERMINAL - TERMINAL TO HOST SYSTEM PROTOCOL DESCRIPTION, dated 11 September 1984.

The operational and diagnostic firmware is documented in the  $\underline{\text{McIDAS}}$  WORKSTATION FIRMWARE DESCRIPTION.<sup>2</sup>

### HARDWARE FUNCTIONAL DESCRIPTION

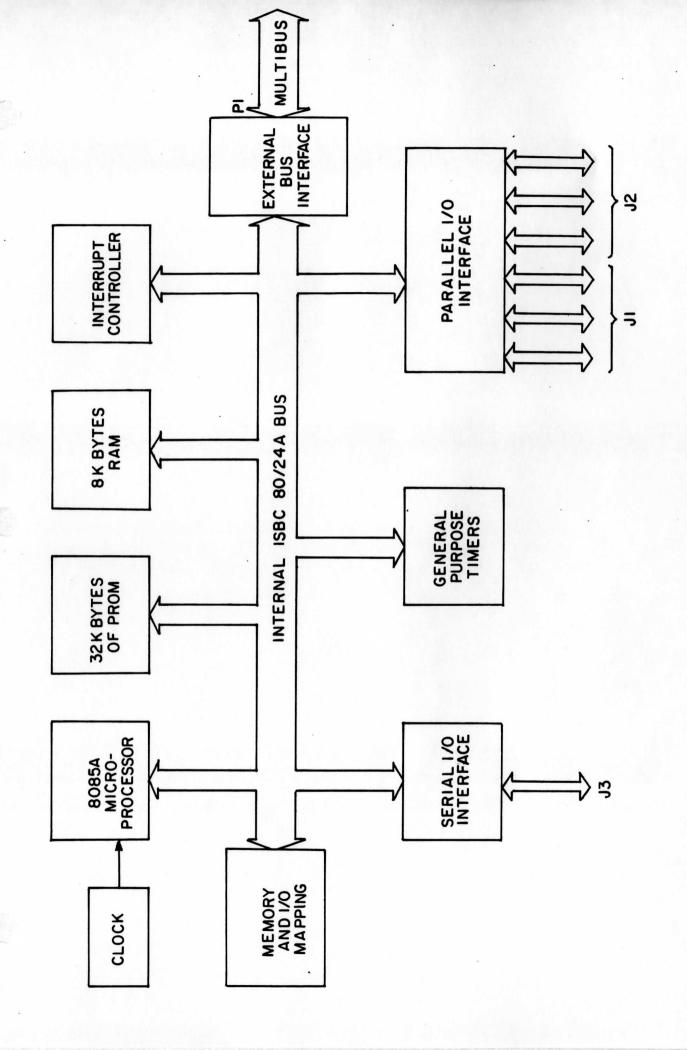

The 80/24A provides the processing power necessary to oversee all Tower processes and maintain a communications link between the PC/AT and the Tower. This board receives data from the PC/AT's MULTIBUS Adapter and steers it to the proper workstation device, and collects status information and data from that device, packing it into a message for transmission to the PC/AT.

$<sup>^{\</sup>mathrm{l}}$  The term "firmware" describes programs stored in non-volatile EPROM that may be altered by the user.

This document is not yet completed. It will be forwarded to you upon completion.

The 80/24A board is built around the Intel 8085A microprocessor chip. The address, data, and control lines of the microprocessor are not only connected to other on-board chips, they are connected to most other electronic control cabinet boards via the MULTIBUS and MULTIBUS interface logic. Note: For additional information on the MULTIBUS, refer to Intel's MULTIBUS DATA BOOK (Order number 210893-003).

The iSBC 80/24A<sup>TM</sup> board (referred to as the "80/24A") is a MULTIBUS-compatible computer system. The board contains 8K bytes of RAM and 32K bytes of erasable-programmable-read-only-memory (EPROM). The board has six 8-bit I/O ports and one programmable serial communications channel.

Figure 1 is a functional block diagram of the iSBC 80/24A.

### MICROPROCESSOR

The microprocessor executes the commands of the workstation firmware package. The microprocessor goes to the EPROM memory block, retrieves the instruction to be executed, and carries out the assigned task. The 8085A microprocessor deciphers the instructions and initiates their execution.

### MEMORY AND I/O MAPPING

All controllable devices external to the microprocessor are assigned a memory address or an I/O address. The Memory and I/O Mapping block in Figure 1 generates the device-enabling signals by processing the microprocessor's address bus output and IO/M control signal. IO/M is high when the microprocessor performs an I/O read or write operation and is low when it performs a memory read or write operation. I/O read and write addressing places an identical binary address on the lower and upper eight bits of the address bus, and represent port addresses of ØØH-FFH (hexadecimal). Memory read and write operations use all 16 address bus lines (ØØØØH-FFFFH). The memory and I/O mapping block only provides address deciphering for on-board memory and I/O devices. Each device external to the 8Ø/24A board (off-board) that is addressable by the microprocessor (via the MULTIBUS) must provide its own memory or I/O mapping logic. The External Bus Interface provides the MULTIBUS with all address and control lines necessary to perform memory and I/O mapping.

FIGURE 1 - MICROPROCESSOR BOARD FUNCTIONAL BLOCK DIAGRAM

The iSBC 80/24A and all other workstation boards and devices are memory and I/O mapped, as shown in Table 1 below.

| 8Ø85 ADDRESS/PORT      | I/O-MEMORY                | FUNCTION                                                                     |

|------------------------|---------------------------|------------------------------------------------------------------------------|

| ØØØH - 5FFFH           | Memory (EPROM)            | Instruction code (80/24A)                                                    |

| 6 <b>000</b> H - 7FFFH | Memory (EPROM)            | Video compression (8024A)                                                    |

| 8ØØØH - 9FFFH          | Memory (RAM)              | BiT 3 Communications Buffer                                                  |

| AØØH - BFFFH           | Memory (RAM)              | General (80/24A)                                                             |

| CØØØH - EFFFH          | Memory                    | Dual channel colorizer enhancement tables                                    |

| FØØØH - FBFFH          | (not used)                |                                                                              |

| FCØØH - FC7F           | Memory                    | DATARAM control addresses                                                    |

| FC8Ø - FEFFH           | (not used)                |                                                                              |

| FFØØH - FF3F           | Memory                    | Graphics enhancement palette                                                 |

| FF4Ø - FF7F            | Memory                    | Cursor enhancement palette                                                   |

| FF8Ø - FFFF            | (not used)                |                                                                              |

| 00 - 37H               | (not used)                |                                                                              |

| 38H - 3FH              | I/O (Input)               | Cursor/Joy Board                                                             |

|                        |                           | Joystick Position Data                                                       |

| 73H                    | I/O (Output)              | TV Timing and Colorizer Graphics Enable                                      |

| 74H-76H                | Not used                  |                                                                              |

| 77H                    | I/O (Input/Output)        | Bisync Control                                                               |

| 78H - 7BH              | I/O (Output)              | Cursor/Joy Board                                                             |

|                        | 710 (7 . 10 )             | Cursor Size and Control                                                      |

| 7CH - 7FH              | I/O (Input/Output)        | BiT 3 MULTIBUS Adapter Board Control                                         |

| 8ØH - 82H              | (not used)                | MV Minima and Calenians - Image Enghle                                       |

| 83H                    | I/O (Output)              | TV Timing and Colorizer - Image Enable                                       |

| 84H - AFH              | (not used)                | TV Timing and Colorizer Vertical Interval                                    |

| 93H                    | I/O Input<br>I/O (Output) | Dual Channel Colorizer - Mask and Control                                    |

| В∅Н                    | 170 (Odipac)              | Register Load                                                                |

| B1H                    | I/O (Output)              | <pre>Dual Channel Colorizer - Mask and Control<br/>Register Load</pre>       |

| В2Н                    | I/O (Output)              | Dual Channel Colorizer - Firmware Backwar<br>Compatibility Support           |

| взн                    | I/O (Output)              | Dual Channel Colorizer - Firmware Backwar<br>Compatibility Support           |

| B4H - D9H              | (not used)                |                                                                              |

| DAH                    | I/O (Input/Output)        | 80/24A Interrupt Controller                                                  |

| DBH                    | (not used)                | od (o. )                                                                     |

| DCH                    | I/O (Input/Output)        | 80/24A - Timer #0 Read/Load                                                  |

| DDH                    | I/O (Input/Output)        | 80/24A - Timer #1 Read/Load                                                  |

| DEH                    | I/O (Input/Output)        | 8 <b>Ø</b> /24A - Timer #2 Read/Load<br>8 <b>Ø</b> /24A - Timer Mode Control |

| DFH<br>Ed. E3          | I/O (Output) (not used)   | 80/24A - Ilmer Mode Control                                                  |

| E <b>Ø -</b> E3<br>E4H | I/O (Input)               | 80/24A - iSBX 351 Baud Rate Select<br>(Line Printer)                         |

| E5H                    | I/O (Input)               | 80/24A - Number of Image Frames                                              |

| E6H                    | I/O (Input)               | 80/24A - Number of Graphics Frames                                           |

| E7H                    | 1/0                       | (Not used)                                                                   |

| E8H                    | I/O (Input)               | 80/24A - Workstation ID Number                                               |

| E9H - EBH              | (not used)                |                                                                              |

| ECH                    | I/O (Input/Output)        | 80/24A - USART Data (CRT)                                                    |

| EDH                    | I/O (Input/Output)        | 80/24A - USART Command/Status                                                |

| EEH-EFH                | 1/0                       | (Not used)                                                                   |

| ГØН                    | I/O (Input/Output)        | 8 <b>0</b> /24A - iSBX 351 USART<br>Command/Status                           |

| F1H                    | I/O (Input/Output)        | 80/24A - iSBX 351 USART Data<br>(Line Printer)                               |

| F2H - F9H              | (not used)                | adday tong and my to a contract                                              |

| FA                     | I/O (Input/Output)        | 80/24A iSBC 351 Timer #2 Control                                             |

| FB                     | I/O (Output)              | 80/24A iSBC 351 Timer Mode Control                                           |

| FC - FFH               | (not used)                |                                                                              |

Table 1. 8085 Memory and I/O Mapping

### **EPROM**

The first 24,576 (0000H - 5FFFH) bytes of EPROM are used by the microprocessor for non-volatile instruction storage. Included in this block are tables and constants. The last 8192 bytes of storage (addresses 6000 - 7FFF) make up a special table used to compress the image data from six bits per pixel to three bits per pixel. The compression process reduces image storage requirements by half.

### RAM

The RAM block is an 8192-byte static RAM. The RAM stores variables, system configuration, status and other scratch pad data.

### SERIAL I/O INTERFACE

The serial I/O Interface block provides a Serial RS-232C communications link to an external device, via the J3 Port. In older style workstations J3 connects to a CRT terminal. The PC/AT replaces the CRT terminal by serving as an intelligent terminal. J3 is used to connect a CRT terminal to the tower during diagnostic testing.

### GENERAL PURPOSE TIMER

The general-purpose Timer block contains three independent timers. The timers are software-programmable and may be configured as frequency generators, interval timers, and real-time interrupt generators.

### PARALLEL I/O INTERFACE

The Parallel I/O Interface block provides six general-purpose 8-bit parallel I/O ports. In McIDAS, only five ports are used. All ports are configured as inputs ports only. Ports E4, E5, and E6 are connected to connector J1 while E8, E9, and EA are connected to connector J2. Programming connectors are connected to J1 and J2, are used to program the selected port input pins. During initialization, performed by the microprocessor immediately after a power turn-on or system reset, the microprocessor reads ports E4, E5, E6, E8 and E9 to determine the following:

- number of video frames port E5

- number of graphics frames port E6

- system AC power frequency (50 hz or 60 hz) port E9

- workstation ID number port E8

#### INTERRUPT CONTROLLER

The microprocessor can directly control four interrupt sources. In McIDAS, all four direct sources are grounded (disabled). The Interrupt Controller block can control eight additional interrupt sources (indirectly). The Interrupt Controller contains an integral priority scheme which arbitrates contention among interrupts. Jumpers connect system interrupts to the selected interrupt priorities. In the McIDAS, three interrupt sources are controlled by the Interrupt Controller. The Vertical Interval on the TV Timing and Colorizer board generates a rate of 30 interrupts per second (INTO/). These interrupts have the highest priority. The CRT Terminal input data is the second highest priority interrupt rate source. Timer #0 generates the programmable interrupt rate with the lowest priority.

For complete configuration of the iSBC 8024A refer to the McIDAS DESIGN NOTE INTEL 8024A Configuration. The design note is part of your original documentation package.

4/PCAT/02

### SECTION 3 12-BIT DUAL CHANNEL COLORIZER - IDT RAM VERSION TABLE OF CONTENTS

| INTRODUCTION                 | -1                          |

|------------------------------|-----------------------------|

| FUNCTIONAL DESCRIPTION       | -1                          |

| DETAILED CIRCUIT DESCRIPTION | -4<br>-4<br>-9<br>-9<br>-12 |

| RAM Enhancement Table        | -13                         |

## 12-BIT (DUAL CHANNEL) COLORIZER - IDT RAM VERSION (SSEC DRAWING 3504-045, DATED 6/24/86)

#### INTRODUCTION

The 12-bit Dual Channel Colorizer performs three major functions on the compressed data from the DATARAM's two image storage units:

- data decompression

- user interaction with image data processing

- user interaction with color enhancement processing

An image picture contains approximately 313,600 pixels, each of which originally is represented by a 6-bit binary code (64 brightness levels). If the 6-bit format is used, over two million bits of storage are required to store each image picture. To reduce storage requirements by half, the 6-bit real data values are compressed into 3-bit "partitions." The microprocessor executes the compression algorithm when it moves the data from the communications buffer to the DATARAM storage unit. The 3-bit partition values are stored in the workstation, reducing the memory requirement by half. Data decompression is the process of reconstituting the 6-bit digital image data from compressed 3-bit partition codes.

Pixel-by-pixel decompression is performed simultaneously on two pictures. Through user interaction, either or both picture(s) can be selected, masked according to video intensity, combined, or processed by combinations of the above actions.

The last major function of the Dual Channel Colorizer is color enhancement of the dual channel video data. The user can define a "gray scale level" to "color hue and brightness" relationship for each video channel individually or for two combined video channels. This function allows a greater volume of image data with more rapid analysis than is possible with a monochrome image.

#### FUNCTIONAL DESCRIPTION

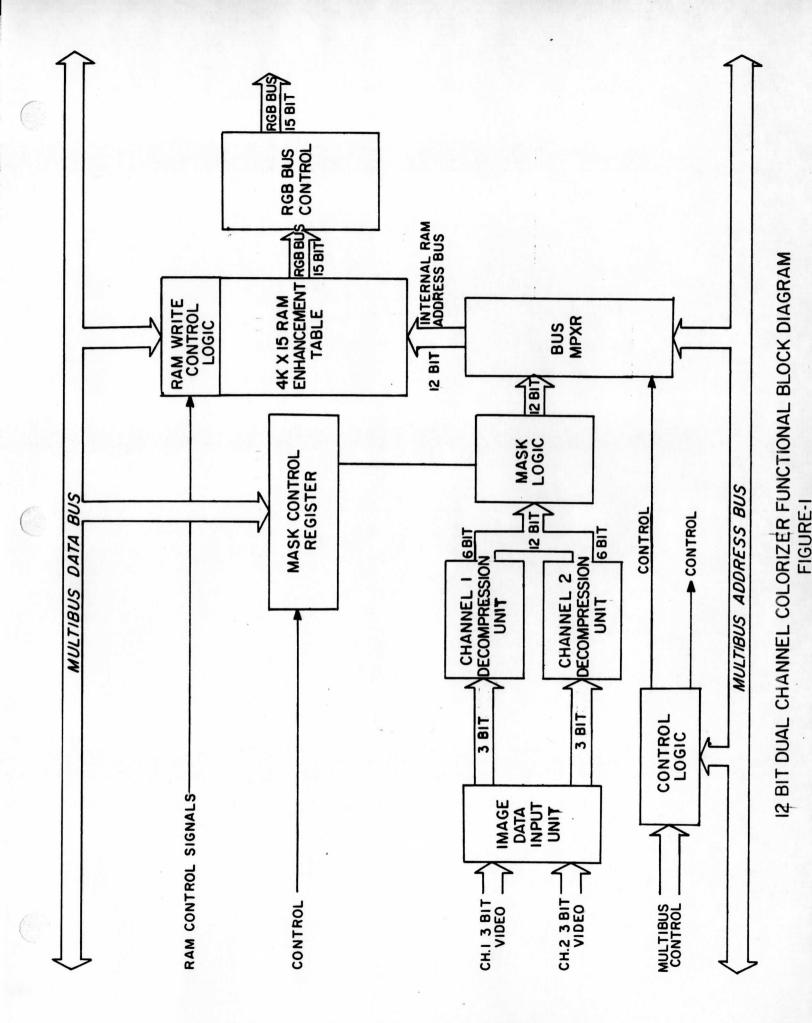

Figure 1 is a functional block diagram of the Dual Channel Colorizer.

The inputs to the Image Data Input Unit are the compressed 3-bit per channel (six bits total) image data from the two DATARAM image storage units. The Image Data Input Unit converts the dual channel input data to TTL logic levels.

Two identical state machines are used to decompress the two 3-bit channels into two 6-bit channels. The only input to the state machines, other than the 3-bit input data, is feedback of the previous 6-bit output data (the previous pixel brightness level).

The 6-bit decompressed data are passed to the Mask Logic block, which can turn off any of the decompressed input data lines via the Mask Control Register block. The output from the Mask Logic block is applied to the Bus Multiplexer block.

The Mask Control Register receives data from the Multibus and latching signals from the Control Logic Unit. The Mask Control Register can store (latch) up to 12 mask control bits used by the Mask Logic Unit. Currently, the Mask Control Register is used as a channel selector, enabling or disabling all data bits of each channel.

The 12-bit output from the Mask Logic Block is applied to one set of inputs of a Bus Multiplexer. The other set of Bus Multiplexer inputs are driven by the Multibus address bus. The Multiplexer output is an address bus for the RAM Enhancement Table. When driven by the Multibus, the multiplexed address bus selects a RAM Enhancement Table cell to be written into. The data to be written into the table cell come from the Multibus data bus. When driven by the Mask Logic Block, the multiplexed address bus selects a cell in the Enhancement Table from which data are read.

The Enhancement Table is a 4K by 15 static RAM and functions as a programmable look-up table. The output of the table is the origin of the RGB (Red, Green, and Blue) bus. The Mask Logic Block output (12-bit, dual-channel, decompressed video) represents video intensity and is applied as an address to the Enhancement Table via the Multiplexer. Note that in single channel operation, six bits are masked off. The 4096 possible combinations of video intensities can address 4096 different 15-bit locations. In each location, five bits are used for each of the three color drives. When the user preprograms the intensities of these colors, each video intensity input corresponds to a particular RGB output.

The RGB Bus Control is a tri-state latch. The latch is controlled by a signal from the TV Timing and Colorizer Board (SSEC 3504-043 sheet 2 of 4). The RGB Bus Control allows the TV Timing and Colorizer board to turn off the RGB bus during the painting of graphics or cursor pixels, thereby assigning the Dual Channel Colorizer image data the lowest priority of the three video data types (image, graphics, and cursor).

The Control Logic block contains line drivers and receivers, memory and I/O mapping, and associated logic circuits that generate the control and gating signals for most of the board.

#### DETAILED CIRCUIT DESCRIPTION

The schematic diagram of the 12-bit Dual Channel Colorizer is shown on SSEC drawing #3504-045 dated 6/24/86). The schematic circuit analysis is accomplished by analyzing groups of components, represented by a single block in Figure 1 above.

#### SCHEMATIC CONVENTIONS

When reference is made to the schematic circuit symbol of a multiple device, the symbol ID number is used, followed by a hyphen and the section letter designator. The symbol ID number alone is used to refer to single section ICs.

#### CONTROL LOGIC

The Control Logic is found on sheet 1 of the schematic diagrams. The primary objective of this Control Logic analysis is to determine which outputs are memory-mapped, which are I/O-mapped, and which addresses activate each signal.

All control signals are derived from two Multibus control signals and the Multibus address bus. The following are Multibus control signals:

- MWTC/ (Memory Write Command, inverted)

- IOWC/ (I/O Write Command, inverted)

The upper eight bits of the address bus are buffered and inverted by octal tri-state buffer J33 (74LS540) and applied to mapping PROM G2 $\emptyset$  (28S42). A list of the six outputs from G2 $\emptyset$ , their addresses, and their primary uses follows:

| Signal | System Addresses  | Prom Address | Prom Output | Primary Use                                            |

|--------|-------------------|--------------|-------------|--------------------------------------------------------|

| MW1/   | CØØ1H-DFFFH(odd)  | 1CØ-1DFH     | FEH         | Enhancement Table Odd (Write)                          |

| MW2/   | CØØØH-DFFEH(even) | ØCØ-ØDFH     | FDH         | Enhancement Table<br>Even (Write)                      |

| IBØ/   | port BØH          | ØвØн         | FBH         | Mask and Control<br>Register Load (Write)              |

| IB1/   | port B1H          | 1B1H         | F7H         | Mask and Control <sup>.</sup><br>Register Load (Write) |

| IB2/   | port B2H          | ØВ2H         | EFH         | *                                                      |

| IB3/   | port B3H          | 1B3H         | DFH         | *                                                      |

<sup>\*</sup> signals exist for firmware support/backward compatibility only.

The Memory Write Control (MWTC/) and I/O Write Control (IOWC/) signals are buffered by octal tri-state buffer G33 (74LS244); they are used along with the six signals from the control mapping PROM to develop the other control signals used throughout the board.

The buffered Memory Write Control command MWT/ (active low) is applied along with the MW1/ signal from PROM G2Ø to OR gate J1Ø-A where they develop the signal MWT1/. This signal is inverted by NAND gate inverter L1Ø-A (74SØØ) and applied to the clocking input of D-latch R8-A. Likewise, the MWT/ signal is applied with mapping PROM signal MW2/ to OR gate J1Ø-B. The output is inverted by L1Ø-B and applied to the clocking input of D-latch T8-A (74S74).

Signals MWT1 and MWT2 control the memory write state of the RAM Enhancement table. MWT1 is active for all odd memory write addresses from CØØ1H-DFFFH while MWT2 is active for all even memory write addresses from CØØØH-DFFEH.

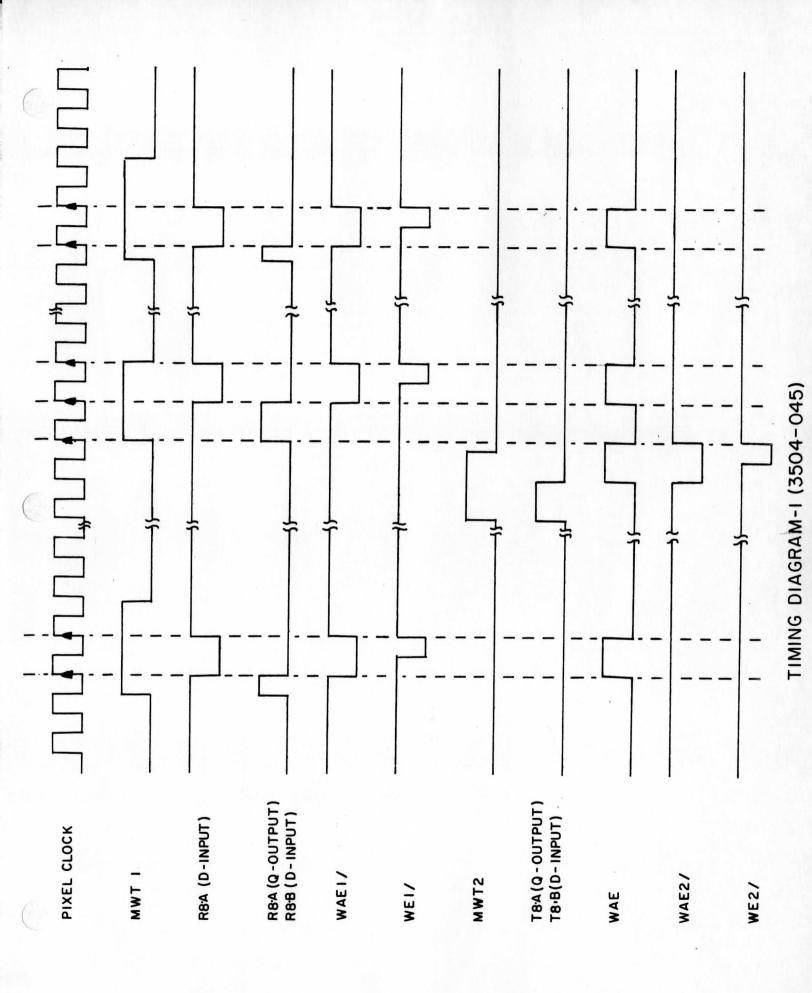

Dual D-latches R8-A and B make up a circuit used to synchronize the memory write enable signal MWTl with the system timing signal PXLCK. Similarly dual D-latches T8-A and B make up a synchronizer for signal MWT2.

Refer to Timing Diagram 1. Signal MWT1 is applied to the clocking input of R8-A. The operation of the synchronizer is best described in terms of the PXLCK signal and its effect on the Dual D-latches' outputs. In a quiescent condition (MWT1 inactive low for several PXLCK pulses).

R8-A and R8-B are both reset. The reset state of R8-B places an inactive high at the CLR input to R8-A and places a high level at its D-input. R8-A's output can only go high if it is clocked by MWT1. R8-B's Q-output can only go high if its D-input goes high prior to a rising edge of PXLCK at its clock input (pin 11).

When the memory write enable MWTl goes active (from low to a high state), it clocks the first D-latch R8-A. The Q output of R8-A changes state and outputs a high level to the D-input of R8-B. On the next rising edge of PXLCK, the high level present at R8-B's D-input is latched into R8-B. A high on the D-input to R8-B causes the Q/ output to change to a low level, applying a low to the D and CLR inputs of R8-A. The low level at R8-A's CLR input causes it to immediately clear. The clearing action of R8-A causes its Q-output to go to a low logic level, which on the next PXLCK is clocked through R8-B to end the cycle.

In effect, the first D-latch, R8-A, is used to set up the operation of the second D-latch, R8-B. WAE1, the Q/ output of the second D-latch is an active low pulse, one PXLCK cycle long, synchronized with the PXLCK signal. To generate a half PXLCK wide write signal (WE1/), R8-B's output is gated through OR gate G1Ø-A by PXLCK before it is applied to the write enable input of the Enhancement RAM.

The MWT2 signal is applied to Dual D-latches T8-A and -B in exactly the same manner as was previously described for the MWT1 signal. D-latches T8-A and -B synchronize the PXLCK signal to the MWT2 signal. WAE2/ (active low) is the synchronized output from T8-B and is applied to OR gate G10-B to generate the write signal WE2/.

The reader should note that what has been accomplished here is the generation of very short (approx. 40 nsec) write pulses for the RAM enhancement table. This minimizes interference with the image display while the enhancement table is being loaded.

The outputs from the clocked OR gates (74S32), WE1/ and WE2/, are the active low memory write enable signals used by the RAM Enhancement Table. Because the Multibus can supply only eight data bits to the RAM at a time, and the table is organized as a 4K by 15-bit RAM, each memory location must be programmed in two write operations. WE1/ (enhancement table odd addresses) loads the Red magnitude and two MSBs of the Green magnitude; while WE2/ (enhancement table even addresses) loads the three LSBs of the Green and all of the Blue magnitude.

WAE1/ and WAE2/ are applied to NAND gate L1Ø-C to develop the WAE signal, used to control the Enhancement Table Address Multiplexer. The WAE signal is applied to the output control pin of octal D-latches X2Ø and Z2Ø. The signal is also applied to a NAND gate L1Ø-D (74SØØ) where it is inverted and applied to the gating inputs of Tri-state buffers L2Ø and J2Ø.

The WAE signal performs two functions: in one state it enables the Mask Logic Block to drive the Address Bus Multiplexer, and in the other state it enables the Multibus to drive the Address Bus Multiplexer. When WAE is high (WAE/ is low), the bus is driven by the Multibus via buffers L2Ø and J2Ø. When WAE is low the latches X2Ø and Z2Ø are enabled and the bus is driven by the Mask Logic Block. The signal WAE/ is active low only during memory writes to addresses CØØØ-DFFFH.

The control PROM's outputs, IBØ/ through IB3/, are used to develop four control signals, MAL/, MAH/, MBL/, and MBH/. Each of the signals IBØ/-IB3/ is ORed with the IOWC/ signal to develop the MAL/-MBH/ signals. The MAx/ signals (high and low block) are applied to the Mask Control Register (R33 and T33, 74LS374) where they are used to clock the masked data bus output to the Mask Logic units. MAL/ clocks R33 (the eight LSBs) while MAH/ clocks T33 (the four MSBs).