Space Sthere

UW SSEC Publication

No. 89.03, M

# McIDAS

Man computer Interactive Data Access System

Ingestors Manual

March 1989

Space Science and Engineering Center University of Wisconsin - Madison 1225 West Dayton Street Madison, WI 53706 Telephone 608-262-2455 TWX 608-263-6738

# MolDAS

Man computer Interactive Data Access System

Ingestors Manual

Marcin 1989

Space Science and Engineering Center Inversity of Wisconsin - Madison 1225 West Dayron Street Medison, Wil 55705 Felaphone 658-2625 WX. 658-263-2455

## **METEOSAT PDUS Ingestor**

| Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| METEOSAT PDUS Ingestor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                                          |

| Basic Functional Description  Figure 1. Simplified Block Diagram of the METEOSAT PDUS Ingestor  Frame Synchronizer Interface Section  Input Buffer Section  Output Buffer Section  Microprocessor Section  Multibus Interface Section                                                                                                                                                                                                                                                                                                                                                                 | 3<br>3<br>4<br>4                                                           |

| Detailed Functional Description Frame Synch Interface Section Byte Selector Interface Controller ID Clock Pulse Inhibitor Input Buffer Section Input Buffers A and B Data Director Controller Figure 2. Detailed Functional Block Diagram of the METEOSAT PDUS Ingestor Address Generators Generator Controller Transfer Controller Output Buffer Section Output Buffers C and D Data Director Controller Address Generators Generator Controller Microprocessor Section Microprocessor Section Microprocessor Lower Address Hatch EPROM RAM Memory and I/O Mapper PIT MUART Clock Multibus Interface | 5 5 5 6 6 6 9 9 9 10 10 10 10 11 11 11 11 11 11 11 11 11 12 12 12 12 12 13 |

Issued 3/89

| C  | ontents                                                     | Page |

|----|-------------------------------------------------------------|------|

| De | etailed Circuit Description                                 |      |

|    | Circuit Labels                                              | 15   |

|    | Logic Conventions                                           |      |

|    | Frame Sync Interface Section                                | 15   |

|    | Byte Selector                                               |      |

|    | Interface Controller                                        |      |

|    | Timing Diagram 1. Frame Sync Interface Controller Timing    | 16   |

|    | ID Clock Pulse Inhibitor                                    | 17   |

|    | Table 1. Input Buffer Controller Signal Characteristics     | 18   |

|    | Input Buffer Section                                        | 19   |

|    | Input Buffers A and B                                       | 19   |

|    | Data Flow Director                                          | 19   |

|    | Input Buffer Controller                                     | 19   |

|    | Table 2. Input Generator Control Signal Characteristics     | 19   |

|    |                                                             |      |

|    | Address Generators                                          | 21   |

|    |                                                             |      |

|    | Transfer Controller                                         | 21   |

|    | Timing Diagram 2. Input to Output Buffer Transfer Controls  | 22   |

|    | Table 4. Output Buffer Controller Signal Characteristics    | 23   |

|    | Table 4. Output Buffer Controller Signal Characteristics    | 24   |

|    | Output Buffer Section                                       | 25   |

|    | C and D                                                     | 25   |

|    | Data Flow Director                                          | 25   |

|    | Controller                                                  | 25   |

|    | Address Generator                                           | 25   |

|    | Table 5. Output Generator Controller Signal Characteristics | 26   |

|    | Controller                                                  | 27   |

|    | Table 6. I/O Ports E1 - E6 Summary                          | 27   |

|    | Microprocessor Section                                      | 28   |

|    | Microprocessor                                              | 28   |

|    | Lower Address Latch                                         | 28   |

|    | Memory and I/O Mapper                                       | 28   |

|    | Table 7. Memory and I/O Map                                 | 29   |

|    | RAM                                                         | 29   |

|    | EPROM                                                       | 29   |

|    | PIT                                                         | 29   |

|    | MUART                                                       | 30   |

|    | Table 8. MUSRT Port I/O Assignments                         | 31   |

|    | Clock                                                       | 31   |

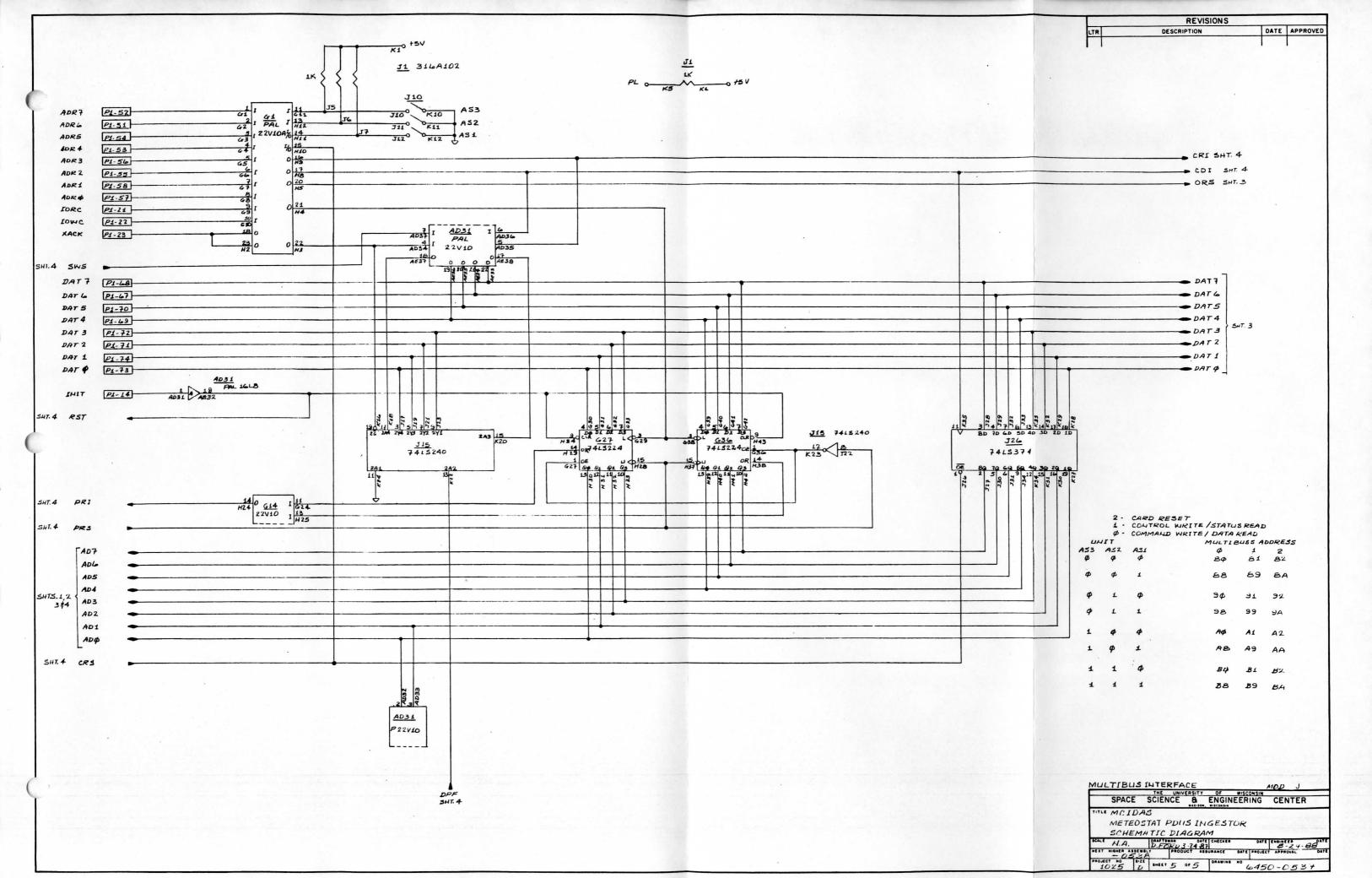

|    | Multibus Interface                                          | 32   |

|    | Multibus I/O Mapper                                         | 32   |

|    | Table 9. I/O Interface Control Signals                      | 33   |

|    | Command Port                                                | 34   |

|    | Status Port                                                 | 34   |

|    | Control Port                                                | 35   |

| Contents                                          | age |

|---------------------------------------------------|-----|

| Supplemental Data                                 |     |

| PAL Equation Listings                             | 37  |

| Symbols and Abbreviations                         |     |

| P22V10 Located at G1                              |     |

| P22V10 Located at G14                             |     |

| P22V10 Located at N32                             |     |

| P22V10 Located at R32                             | 44  |

| P22V10 Located at X32                             |     |

| P22V10 Located at Z32                             |     |

| P22V10 Located at AD31                            |     |

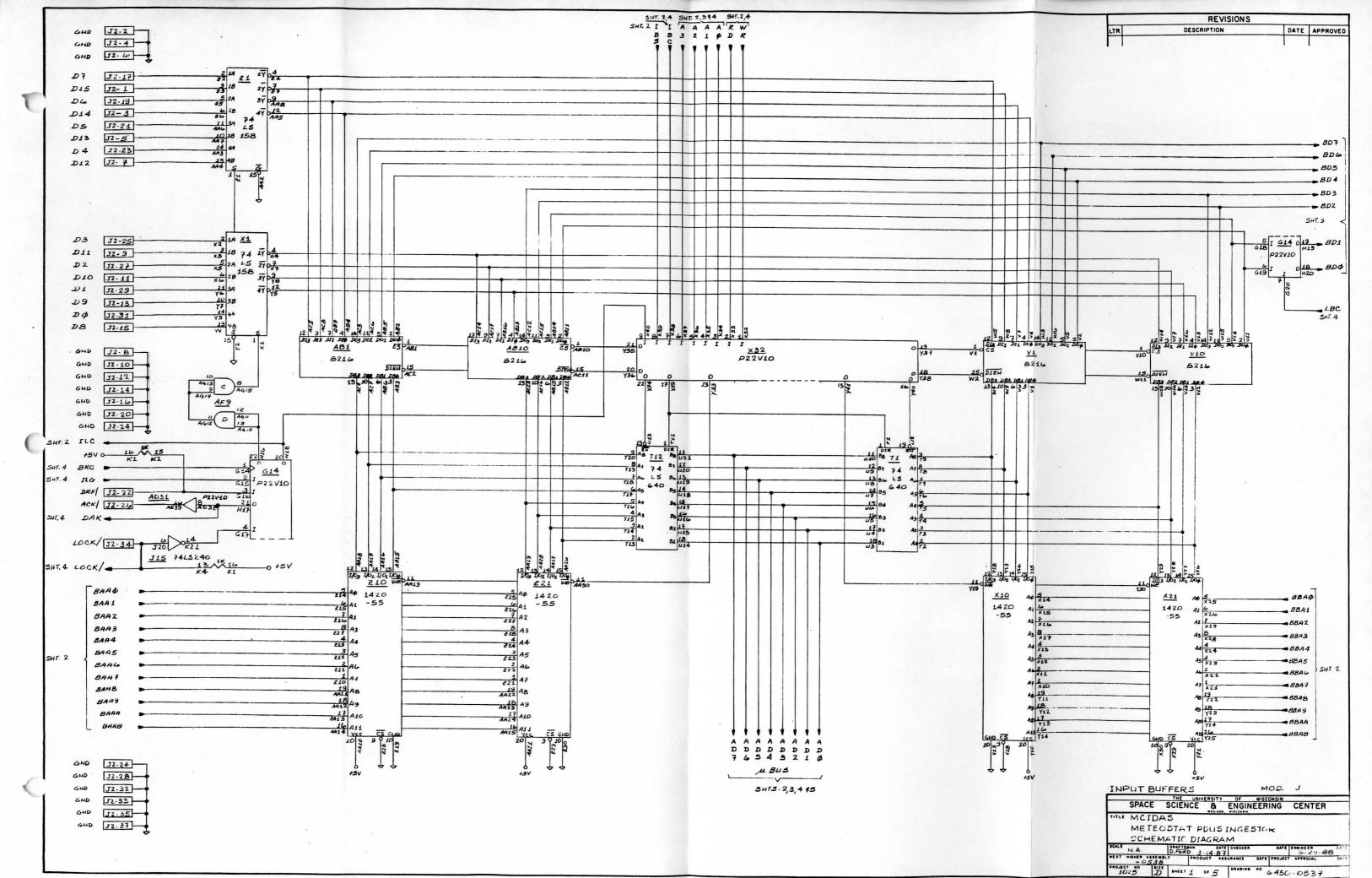

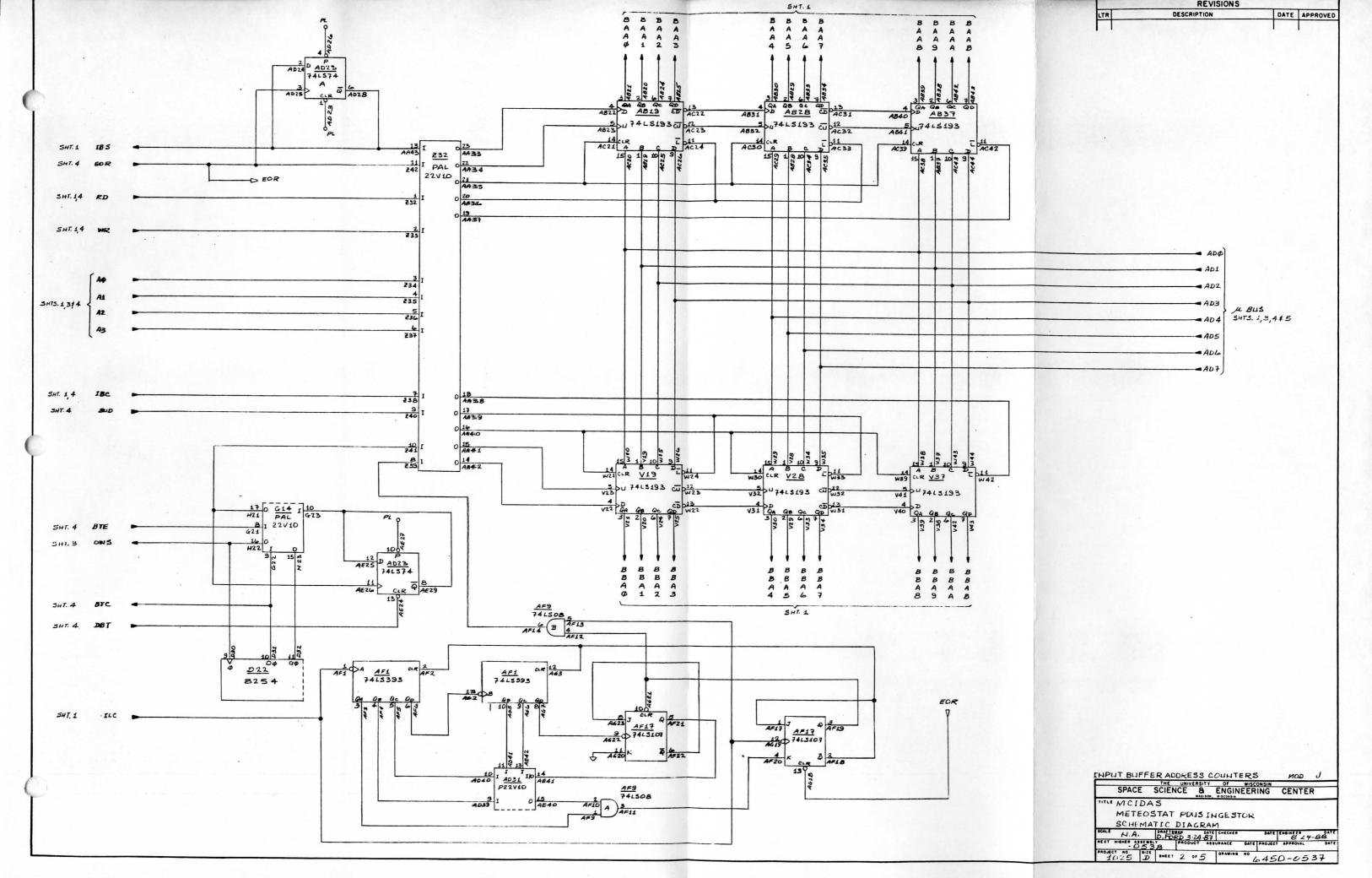

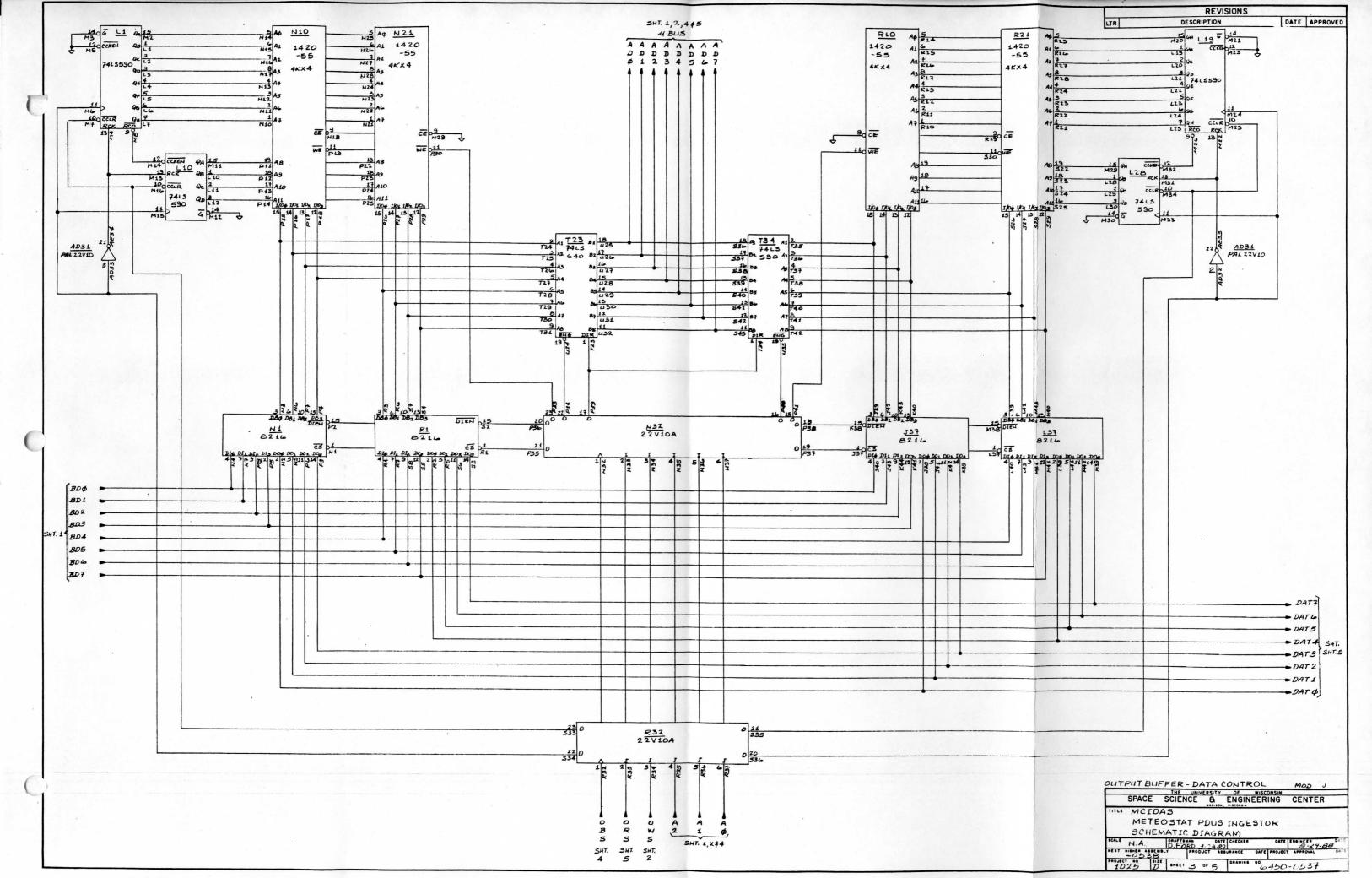

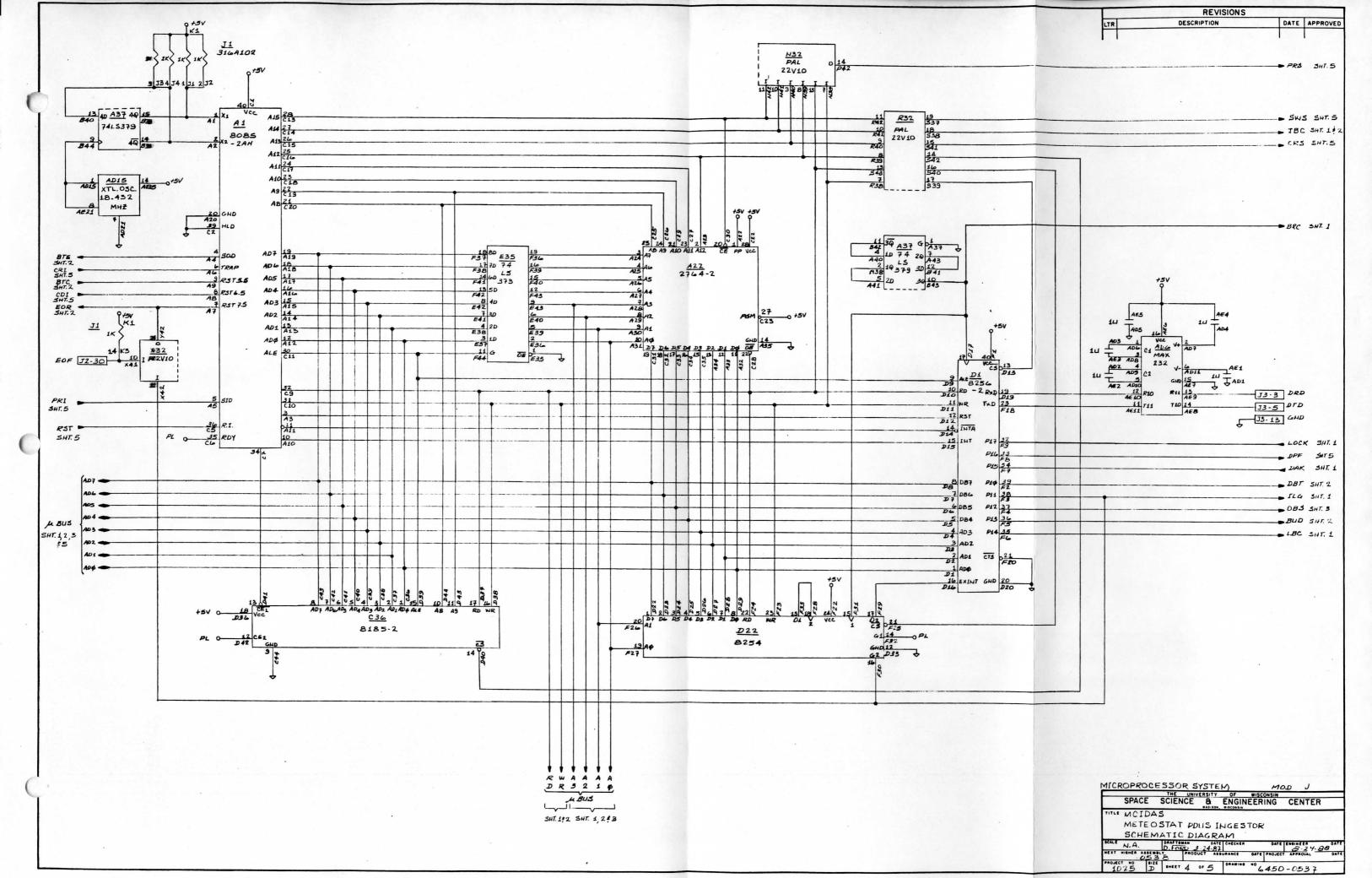

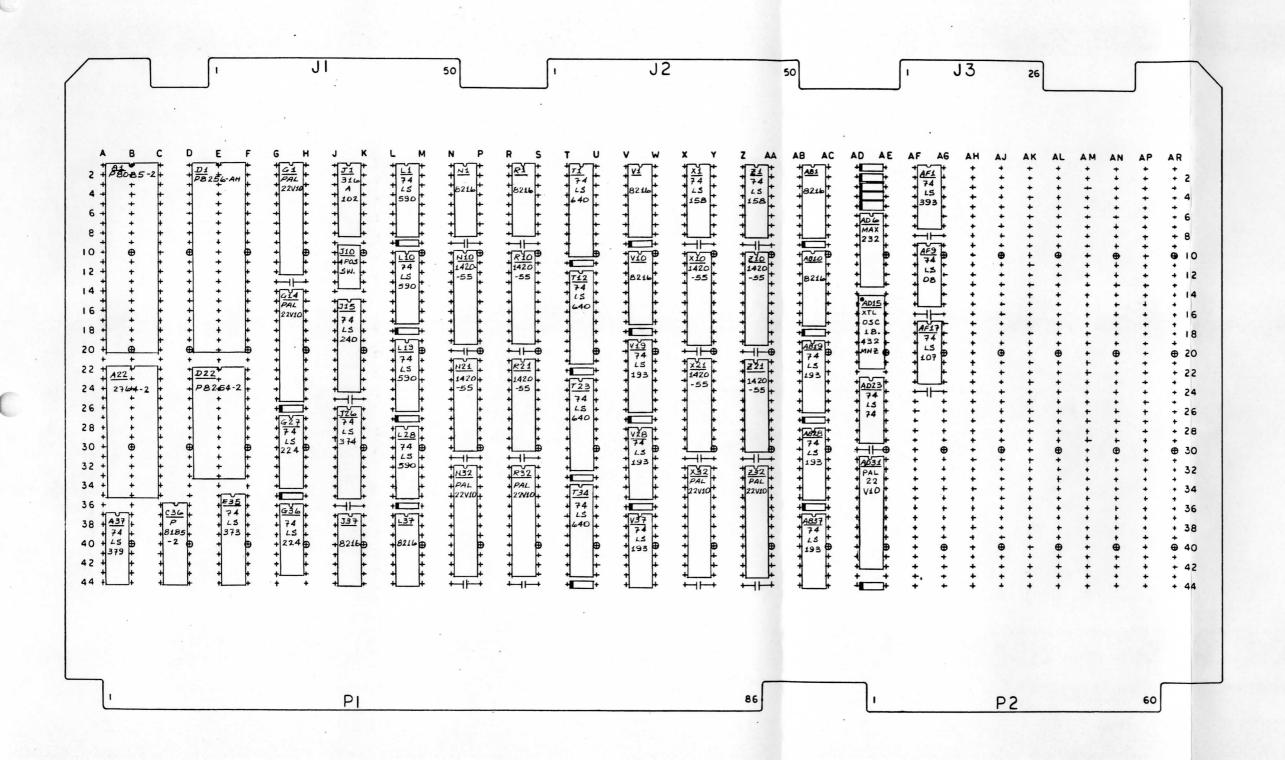

| Schematic Drawings 1 - 5                          | 50  |

| Assembly Drawing 1                                |     |

| Appendix A                                        |     |

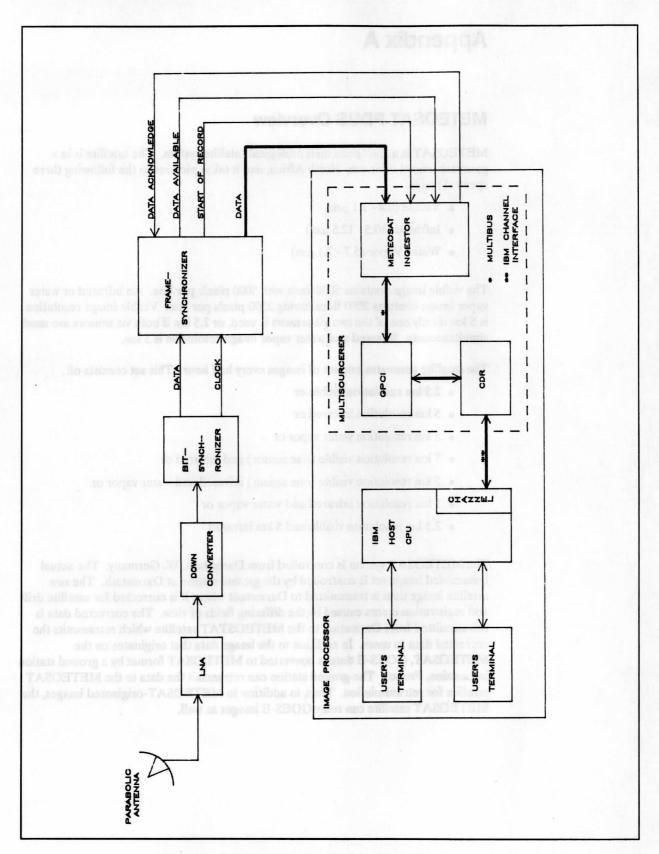

| METEOSAT PDUS Overview                            | A-1 |

| Figure 1. Primary Data User Station Block Diagram | A-2 |

| Block Diagram                                     |     |

| Table 1. Modes A and B Data Format Summary        |     |

| METEOSAT Data Characteristics                     |     |

| Data Format                                       | A-5 |

| Heading Subframes                                 |     |

| Image Data Subframes                              |     |

| Annotation Subframes                              |     |

| Conclusion Subframe                               |     |

Issued 3/89

Property for the second second

iv

## **Reader Response**

We would like your comments on our manual. Please take a moment to fill out this self-mailing form and return it to SSEC - McIDAS User Services and Documentation. Thank you for your help.

| Manual name     | (Irom t   | ne title p | age)      |            |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|-----------------|-----------|------------|-----------|------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Did you find t  | his man   | ual helpf  | ul? Did   | it provid  | e the requ | aired information?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                 |           |            |           |            | oreH bi    | Pol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Did you find e  | errors or | omissio    | ns in the | manual?    | Please be  | e very specific.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Please rate thi | s manua   | al on the  | following | g items fr | om 1 to 5, | , with 1 as low and 5 as high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Text            | 1         | 2          | 3         | 4          | 5          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Graphics        | 1         | 2          | 3         | 4          | 5          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Ease-of-use     | 1         | 2          | 3         | 4          | 5          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Overall         | 1         | 2          | 3         | 4          | 5          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| What is the be  | st featur | re of this | manual?   |            |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                 |           |            |           |            |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| What is the wo  | orst feat | ure of thi | s manua   | 1?         |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                 |           |            |           |            |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Your name and   | d title   |            |           |            |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Date            |           |            |           |            |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| McIDAS site     |           |            |           |            |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Address         |           |            |           |            | day of the | was subject to the su |  |

|                 |           | noises     | DOM:      | ACL hos    | reniume    | Mell) A.S. I Iser S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Telephone       |           | -          | 0.00      | ibeld -    | History)   | Wite raily of W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Check here if v | ייטע ווסע | ld like a  | written = | enly       |            | Madison, WI 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

Reader Response

Fold Here Fold Here

> Space Science and Engineering Center McIDAS User Services and Documentation, Room 611 University of Wisconsin - Madison 1225 West Dayton Street Madison, WI 53706

1

## **METEOSAT PDUS Ingestor**

METEOSAT is the European meteorological satellite system. Appendix A describes the METEOSAT system and a typical Primary Data User Station (PDUS). A PDUS uses the processed and retransmitted high resolution digital METEOSAT data.

The METEOSAT Ingestor card (hereafter referred to as "ingestor") is a Multisourcerer application card. It functions as an intelligent interface between a Dornier Frame Synchronizer and the internal Multibus\* of the Multisourcerer.

The raw satellite data is processed, formatted into "records", and retransmitted to the METEOSAT satellite. The satellite broadcasts the data serially on an S-band microwave channel to METEOSAT users. The PDUS receiving and demodulating system recovers the serial data bits. This data is passed to the Dornier Frame Synchronizer (frame sync). The frame sync forms the serial data bits into 16-bit parallel words. Each 16-bit word represents two bytes of data. The ingestor collects the words and reconstructs them into data records. It does this by separating the 16-bit words into bytes and storing them in one of two input buffers.

When the entire data record has been assembled, the input buffers are swapped, making an empty input buffer available for the next incoming record. While the next record is being assembled, the previous record is transferred to the host.

The following documentation assumes that you are familiar with Appendix A and 8085 microprocessor applications.

This document is divided into three areas of discussion:

- Basic Functional Description

- Detailed Functional Description

- Detailed Circuit Description

\*MULTIBUS is a registered trademark of INTEL Corporation.

Issued 3/89

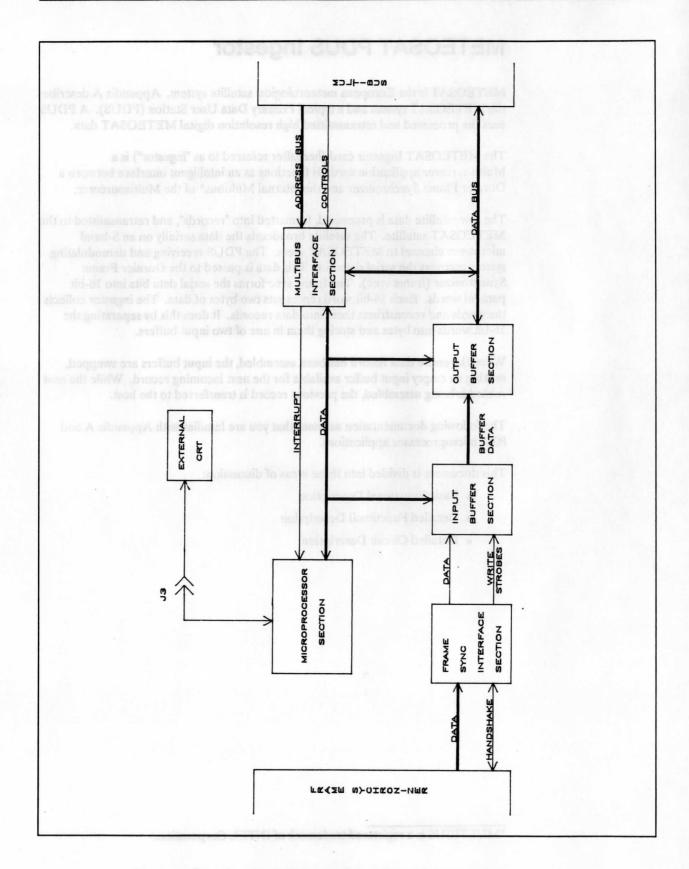

Figure 1. Simplified Block Diagram of the METEOSAT PDUS Ingestor

## **Basic Functional Description**

Figure 1 on the adjacent page is the Simplified Functional Block Diagram of the PDUS METEOSAT Ingestor. The ingestor is divided into the following five functional parts:

- Frame Synchronizer Interface Section

- Input Buffer Section

- Output Buffer Section

- Microprocessor Section

- Multibus Interface Section

## Frame Synchronizer Interface Section

The Dornier Frame Synchronizer converts the serial data stream input to a parallel output. METEOSAT data is eight bits per word. The frame sync sends two words (16 bits) at a time to the ingestor via a 16-bit parallel bus. Handshake signals control the data transmission process.

The Frame Sync Interface Section separates the 16-bit input words into two 8-bit words, and sends these words to the Input Buffer Section. The Frame Synchronizer Interface Section also develops an input load strobe for each word it transfers to the Input Buffer Section. Two input load strobes are generated for each 16-bit input word.

## **Input Buffer Section**

The Input Buffer Section consists of two buffers. Each buffer can function as either an on-line buffer or an off-line buffer. The on-line buffer receives satellite input data while the off-line buffer passes its previously stored data to the Output Buffer Section. When reception of the current incoming record is complete, the buffers swap functions. That is, the on-line buffer becomes the off-line buffer and vice versa.

## **Output Buffer Section**

The Output Buffer Section is nearly identical to the Input Buffer Section. It has two buffers that function as either on-line or off-line buffers. The off-line buffer receives data from the off-line input buffer while the on-line buffer transfers data to the Multibus. When both output buffers complete their respective transfer, the buffers swap functions.

Issued 3/89 3

## **Microprocessor Section**

The Microprocessor Section is a conventional 8085 design. It functions as the board controller. The following are primary functions performed by this section:

- input buffer switching

- output buffer switching

- diagnostic testing of other ingestor sections

- data transfer control

- asynchronous communications with an external CRT

- Multibus interface control

### Multibus Interface Section

The Multibus Interface Section makes the ingestor appear (from the Multibus' perspective) as a group of I/O ports. The Multibus writes commands and controls into two of these ports. The ingestor reads the commands and controls to determine what data is requested. The ingestor informs the Multibus of its progress in acquiring the requested data via a status port. The Multibus periodically reads ingestor status to determine when the ingestor has the requested data ready. When the Multibus is ready to receive the requested data, it sends the ingestor a command instructing it to send the data.

## **Detailed Functional Description**

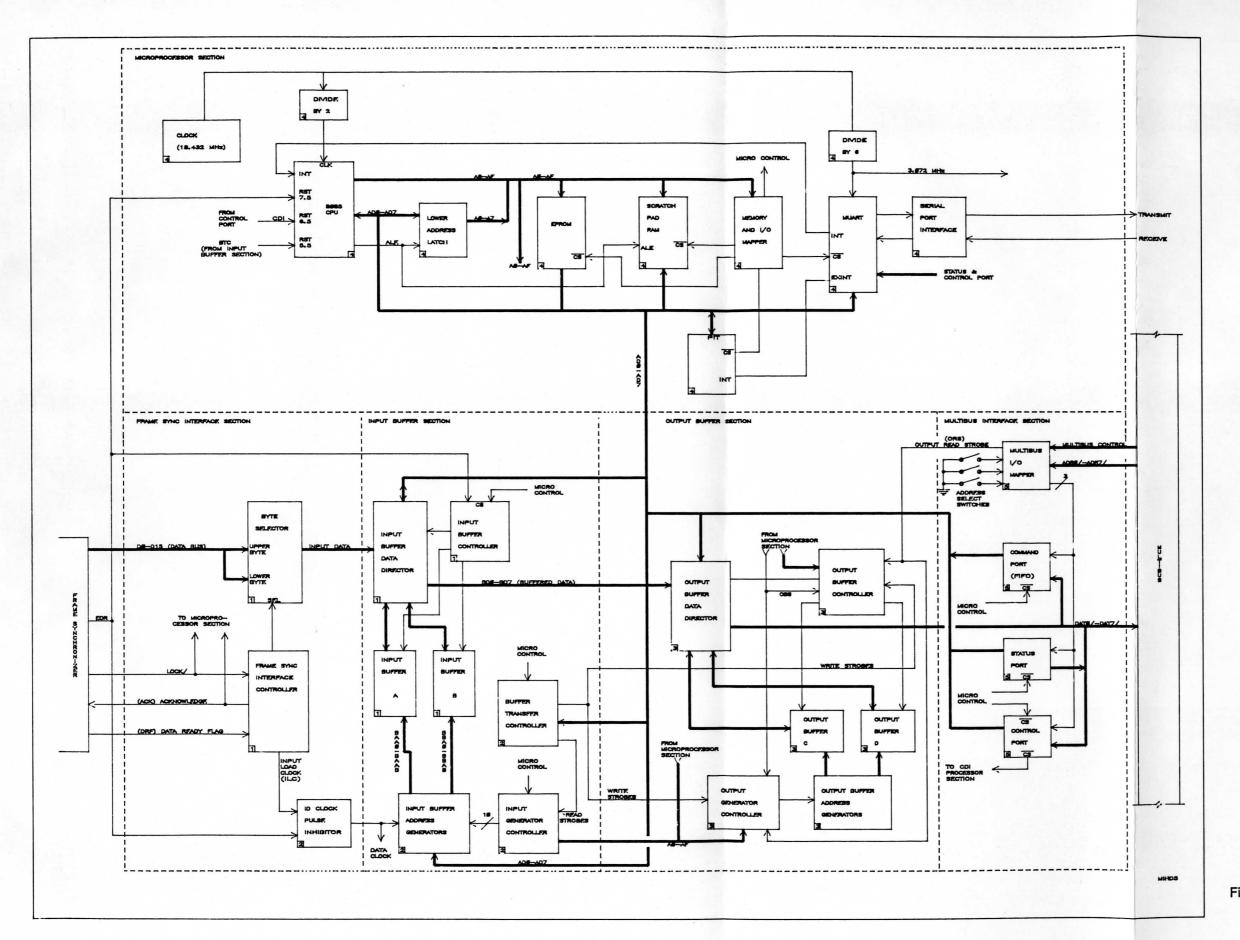

The Detailed Functional Block Diagram of the PDUS METEOSAT Ingestor is shown in Figure 2 on the page 7. This figure is an expansion of Figure 1, and introduces the main control blocks. Note that the schematic sheet numbers are listed in each functional block. This should make the transition from the Functional Descriptions to the schematic diagrams easier.

This detailed functional description includes:

- Frame Sync Interface Section

- Input Buffer Section

- Output Buffer Section

- Microprocessor Section

## Frame Sync Interface Section

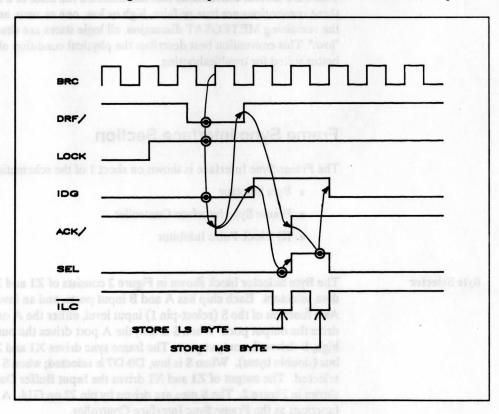

Before discussing the Frame Sync Interface Section, a few Dornier Frame Synchronizer characteristics should be reviewed. The Dornier Frame Synchronizer assembles the serial data output of a bit synchronizer into double-byte words (16 bits total). It sends these words to the ingestor via a 16-bit parallel bus. When the 16-bit word is valid and stable on the parallel bus, the frame sync sets the Data Ready flag (DRF). DRF remains active until the ingestor responds to the flag by activating the Acknowledge (ACK) signal.

**Byte Selector**

The 16-bit frame sync words must be disassembled into two 8-bit words because all ingestor buffers and buses are eight bits wide. The Byte Selector, under control of the Frame Sync Interface Controller, performs this function.

**Interface Controller**

DRF goes true after the data on the 16-bit input bus is valid. While the data is valid, the Frame Sync Interface Controller performs two Buffer Memory transfers. First, it transfers the least significant byte of the 16-bit word, then it transfers the most significant byte. The Frame Sync Interface Controller generates the Buffer Memory transfer strobes (Load Clock in Figure 2), and manipulates the SEL (select) input to the Byte Selector during the transfer.

The Frame Sync Interface Controller manages the ingestor's side of the handshake scheme between the ingestor and the frame sync. Essentially, this consists of returning an ACK (Acknowledge) after receiving a DRF flag. The ingestor holds ACK until DRF goes false.

ID Clock Pulse Inhibitor Refer to Appendix A, if necessary. The Dornier Frame Sync strips off the three sync words located at the beginning of each frame. It sends the remaining 361 bytes of each frame to the ingestor. The first byte of each 361-byte frame is the ID word. The ID word is not used, and must also be stripped off before storing the frames in the Input Buffer.

> The ID Clock Pulse Inhibitor receives input Load Clock pulses from the Frame Sync Interface Controller. It inhibits the first clock pulse in each 361-byte frame. The Input Buffer Address Generator uses the output of the ID Clock Pulse Inhibitor as memory write strobes for the Buffer Memory. Since the ID words' clock pulses are inhibited, the ID words are not stored in the Buffer Memory.

The ID Clock Pulse Inhibitor is initialized every eight frames (A-Format) or every four frames (B-Format) by EOR (End of Record). The frame sync generates the EOR signal, marking the end of the current subframe and the beginning of the next subframe. EOR also generates a restart interrupt for the microprocessor. The function of this interrupt is discussed further in the Microprocessor Section.

## Input Buffer Section

The Input Buffer Section stores input data from the Frame Sync Interface Section. It transfers data to the Output Buffer when enabled by the Microprocessor Section.

#### Input Buffers A and B

Each Input Buffer is a 4K by 8-bit static RAM. Each buffer can function as either the on-line or off-line buffer. These functions are toggled by EOR. That is, at the end of each record the on-line buffer becomes the off-line buffer, and the off-line buffer becomes the on-line buffer. Input data is stored in the on-line buffer while the off-line buffer's data is transferred to the Output Buffer Section.

#### **Data Director**

The Input Buffer Data Director receives input data from the Frame Sync Interface Section and the Microprocessor Section. The Input Data Bus (see Figure 2) transports the lower byte, then the upper byte, from the Frame Sync Interface to the Input Buffer Data Flow Director. The Input Buffer Data Director sends either the Selected Data or microprocessor data to the on-line buffer (A or B). The microprocessor writes data to the Input Buffer Section during diagnostic testing.

The Input Buffer Data Director passes data from the off-line input buffer to the Microprocessor Section or the Output Buffer Section. It passes data to the microprocessor during diagnostic testing and data ingesting.

#### Controller

The Input Buffer Controller performs the following control functions:

- enables the data source in the Input Buffer Data Director to the online buffer

- generates write strobes for the on-line and off-line buffers

- gates the off-line buffer data to the selected destination

Figure 2. Detailed Functional Block Diagram of the METEOSAT PDUS Ingestor

#### **Address Generators**

The Input Buffer Address Generators block consists of two 12-bit programmable up/down binary counters. One counter drives the address inputs of Input Buffer A. The other drives the inputs of Input Buffer B. Each counter has the following control inputs from the Input Generator Controller:

- clear

- count up clock

- countdown clock

- lower byte load

- upper nibble load

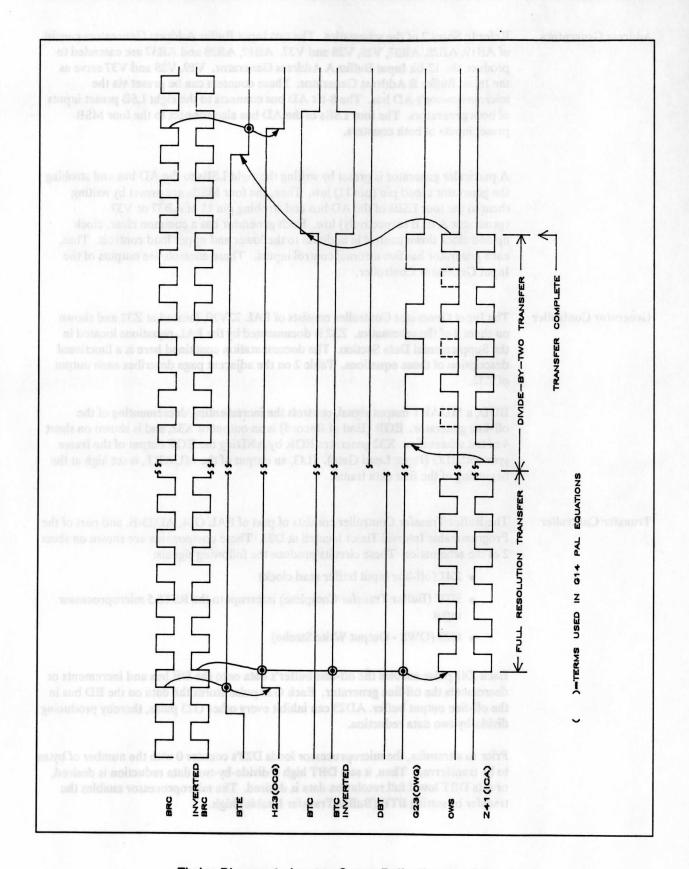

The on-line Input Buffer Address Generator is always cleared (reset to 000H) prior to the arrival of the first byte of a new record. The on-line generator is always in the count up mode. However, the off-line Input Buffer Address Generator is usually preset (loaded) with the address of the last stored byte, and the generator is operated in the countdown mode.

The METEOSAT satellite physically scans from east to west and south to north. Since most image monitors scan from left to right and top to bottom, images would appear upside down and backwards if the data was used in the same chronological order as generated. The mainframe reverses the south to north effect; the ingestor reverses the east to west effect. The east to west effect is corrected by storing data in the on-line input buffer in ascending address order, and outputting this data in descending address order.

#### **Generator Controller**

The Input Generator Controller produces the five control signals listed above for each counter. This block receives control and data inputs from the Microprocessor and Frame Sync Interface Sections. The Microprocessor Section controls the up/down mode of the off-line buffer's address generator. Microprocessor read/write controls produce appropriate up/down clock pulses for the address generators during microprocessor read/write cycles. Load Clock pulses from the Frame Sync Interface produce clock up pulses for the on-line Input Buffer Address Generator. Finally, counter offsets, required when reading the off-line buffer backwards, are transported to the Input Generator Controller by the microprocessor's AD bus.

#### **Transfer Controller**

The Buffer Transfer Controller controls the record transfers from the off-line Input Buffer to the off-line Output Buffer. The heart of this block is a programmable 16-bit counter. Prior to the start of a transfer, the microprocessor loads the counter with the number of bytes to be transferred. Then, the microprocessor enables the block via a control signal from its MUART, allowing the transfer to commence. The block has three outputs, an off-line Input Buffer read strobe, an off-line Output Buffer write strobe, and a Buffer Transfer Complete (BTC) interrupt for the microprocessor. The read and write strobes are generated at a 3.072 MHz rate until the counter decrements to zero. When the counter reaches zero, the transfer ceases and BTC goes active, interrupting the microprocessor. The interrupt informs the microprocessor that the transfer is complete, allowing the microprocessor to remove the transfer enable signal.

## **Output Buffer Section**

The Output Buffer Section is functionally and physically very similar to the Input Buffer Section.

Output Buffers C and D Output Buffers C and D are physically identical to Input Buffers A and B. The off-line output buffer receives input data from the off-line input buffer (via the Output Buffer Data Director). The on-line/off-line functions are toggled by OBS (Output Buffer Switch). OBS is a control signal output of the MUART and is controlled by the microprocessor.

#### **Data Director**

The Output Buffer Data Director receives data from the Input Buffer and Microprocessor Sections. The Output Buffer Data Director sends data to the off-line buffer. During diagnostic testing, the microprocessor can write data to either the on-line or off-line buffer.

The Output Buffer Data Director gates data from the on-line output buffer to either the Multibus or the Microprocessor Section (diagnostic testing only).

#### Controller

The Output Buffer Controller performs the following control functions:

- gates the selected data to the off-line buffer

- generates write strobes for the off-line buffer

- gates on-line buffer data to the selected destination

#### **Address Generators**

The Output Buffer Address Generators generate addresses for Output Buffers C and D. Each buffer has its own generator. These generators always begin at address 000H and can only be incremented. Thus, they are physically and functionally simpler than their Input Buffer Section counterparts. Each generator has the following control inputs:

- clear

- clock (up)

The respective generator is always reset to zero prior to the start of a transfer. The counters are incremented after each byte transfer.

#### **Generator Controller**

The Output Generator Controller produces the clear and clock input for each address generator. OBS determines the off-line and on-line buffers. ORS (Output Read Strobe) causes the Output Generator Controller to generate a clock pulse for the on-line generator after each Multibus I/O read cycle. Write strobes from the Input Buffer Section cause the Output Generator Controller to generate clock pulses for the off-line generator after each byte transfer.

## **Microprocessor Section**

The Microprocessor Section is conventional in design. The design is based on the Intel 8085 microprocessor.

#### Microprocessor

The hardware aspect of the 8085 microprocessor is well documented in Intel's *Microprocessor and Peripheral Handbook*. The *Intel 8080/8085 Assembly Language Programming* manual provides a good programming reference for the 8085. The additional 8085 hardware documentation provided here is limited to that which is necessary to discuss remaining Microprocessor Section components.

The 8085 has three restart interrupt inputs. They include RST5.5, RST6.5 and RST7.5. All three are used in the METEOSAT application. The restart interrupts allow hardware to force the 8085 into an interrupt service routine. Upon completion of the service routine, the 8085 returns to the point in the program from which it was interrupted. BTC drives the RST5.5 interrupt, and interrupts the 8085 upon completion of an off-line input buffer to off-line output buffer transfer. The RST6.5 interrupt is driven by the Control Port. The Control Port automatically generates an interrupt (CDI) when the Multibus writes to it. RST7.5 allows the End of Record (EOR) signal, initiated by the frame sync, to interrupt the 8085 at the end of a record.

#### Lower Address Latch

The 8085 multiplexes data with the lower eight bits of the address and outputs this information on its AD bus (AD0-AD7). The 8085 outputs a demultiplexing control signal called ALE (Address Latch Enable). ALE is high when the multiplexed address/data bus carries valid address information. The Lower Address Latch is driven by the AD bus; it is latched by ALE. Thus, the output of the latch is the lower eight address bits. The upper eight address bits are output directly from the address port on the 8085. This port joins the output of the Lower Address Latch to form the 16-bit address bus (A0-AFH). This bus drives the EPROM, Scratch Pad RAM, and the Memory and I/O Mapper. Each of these devices is discussed separately below.

#### **EPROM**

The 8K by 8-bit EPROM (Erasable Programmable Read-Only Memory) stores the ingestor's firmware. The 13 LSBs of the A bus (A0-AC) drive the address inputs. The EPROM's output connects to the microprocessor's AD bus.

#### **RAM**

The RAM (Random Access Memory) provides temporary storage for the following system variables:

- microprocessor's stack

- data record label

- CRT message buffers

- program pointers and flags

The RAM has a multiplexed address/data port, and is connected directly to the AD bus. The ALE output of the microprocessor demultiplexes the addresses and data. The RAM's two MSB address inputs are driven by A8 and A9 of the A bus.

Memory & I/O Mapper

The Memory and I/O Mapper produce chip enable signals for each device addressable by the microprocessor. This block produces chip enables for the following:

- EPROM

- RAM

- Programmable Interval Timer (PIT)

- Control Port

- Status Port

- Input Buffer Controller

- Command Port

- MUART

PIT

The PIT (Programmable Interval Timer) has three independent 16-bit programmable counter/timers. One counter/timer functions as an event counter, counting the number of bytes transferred from the off-line input buffer to the off-line output buffer. It is part of the Buffer Transfer Controller (refer to the Input Buffer Section). The remaining two counters are cascaded to produce a 32-bit counter. The output of the first counter drives the input of the second counter.

The cascaded counter generates an interrupt if the frame sync takes more than 90 seconds to acquire a signal after receiving an IDLE command. The IDLE Command instructs the ingestor to wait for the RST 7.5 EOR interrupt.

MUART

The MUART (Multifunction Universal Asynchronous Receiver Transmitter) combines several microprocessor functions into a single LSI chip. This chip provides:

- five 8-bit programmable timer/counters

- a programmable serial asynchronous communications interface

- an on board baud rate generator

- two 8-bit programmable parallel I/O ports

- an eight level priority interrupt controller

The timer/counters are numbered 1-5. Timer/counter 1 is not used. Timer/counters 2 and 4 are cascaded, yielding a 16-bit timer. They are used as the SYNC command timeout counter. The ingestor informs the host when it begins receiving header records. The host may issue a SYNC command which tells the ingestor to wait for the first data record. Up to 84 2912-byte header records may be received before the data records begin (see Appendix A). The firmware shuts off the SYNC timeout counter when a data record is received.

Timer/counter 3 functions as the WAIT command timeout counter. The WAIT command tells the ingestor to wait for the next data record. The host issues WAIT commands when the current data record is not required by the host.

Timer/counter 5 functions as a retriggerable counter. It is reset (retriggered) by ACK, the ingestor's response to the frame sync's input data. Thus, if the frame sync stops sending data, no ACKs are generated, and timer 5 times out, causing an interrupt.

The programmable serial asynchronous communications interface provides an interface to a CRT. It can monitor host commands and display record labels and ingestor status. It is not required for ingestor operation.

The on board baud rate generator generates a baud rate clock for the programmable serial asynchronous communications interface. It can generate 13 standard baud rates, ranging from 50 baud to 19.2K baud. Currently, it is programmed for 19.2K baud.

The MUART has two 8-bit programmable I/O ports. Only Port 1 is currently used. Each I/O pin on Port 1 can be individually defined as an input or output pin. The pins that are defined as output pins are used as control inputs to other sections of the ingestor; the pins that are defined as inputs provide status inputs from other sections of the ingestor.

The eight level priority interrupt controller assigns priorities to the following interrupt sources:

- port 1 (highest priority)

- external interrupt (EXINT)

- timer 3

- · asynchronous receiver buffer full

- · asynchronous transmitter buffer empty

- timer 2 and 4 (cascaded)

- timer 5 (lowest priority)

The eight level priority interrupt controller prevents interrupt source contention during simultaneous interrupts. INT, the output of this section, drives the INT input on the microprocessor. The microprocessor executes an interrupt service routine for the device causing the interrupt.

Clock

The Clock generates an 18.432 MHz square wave. This signal frequency is divided by two to produce a 9.216 MHz clock input for the microprocessor. The Clock output drives a divide-by-six circuit to produce a 3.072 MHz clock for the MUART and Input Buffer Controller.

#### **Multibus Interface**

The Multibus Interface section makes the ingestor appear (from the Multibus' perspective) as a group of I/O ports. A switch-programmable I/O address decoder responds only to Multibus I/O activity intended for this ingestor. It generates enable signals for the three I/O ports addressable by the Multibus. Each I/O port has a unique address within the block of I/O addresses selected by the address decoder. The three I/O ports are:

- Control and Status Port

- Command and Data Out Port

- Soft Reset Port

The Control and Status port is actually two I/O ports that share the same I/O Port address. The Control Port responds to Multibus write cycles and the Status Port responds to Multibus read cycles. The Multibus writes to the Control Port which is read by the microprocessor. The Control Port hardware automatically interrupts the microprocessor when the Multibus writes to it. The Multibus can tell the microprocessor to either abort the last command or read a new command that is just written to the Command Port. The microprocessor writes to the Status Port. This port is read by the Multibus, and allows the GPCI to monitor progress of the previous command.

The Command and Data Out Port is actually two I/O ports that share the same I/O port address. The Command Port responds to Multibus write cycles and the Status Port responds to Multibus read cycles.

The Multibus writes to the Command Port which is read by the microprocessor. The Command Port can store commands up to 16 bytes in length. However, writing to the Command port has no effect on the microprocessor. That is, it does not generate an interrupt. The microprocessor must be informed of the new command by writing an appropriate control word to the Control Port (see the preceding paragraph) after writing the command.

The Data Out Port passes image data to the GPCI. First, the ingestor transfers an image data record from its Input Buffer to its Output Buffer, making the data available to the GPCI. Then, the ingestor sets the Data Present flag in the Status Port. The GPCI polls the Status Port periodically, and upon detection of the Data Present flag, performs a DMA transfer from the Data Out Port to the GPCI.

The Soft Reset Port allows the GPCI to reset the METEOSAT PDUS Ingestor. The GPCI issues a soft reset when it receives unexpected results for commands issued to the ingestor.

## **Detailed Circuit Description**

The schematic diagrams of the METEOSAT PDUS Ingestor are shown on SSEC drawing #6450-0537 (Revision H, dated 1/7/88).

#### **Circuit Labels**

The METEOSAT Ingestor is built on a Multibus wire-wrap form factor board. Pin locations on the board are described by the column designator (alpha) and the row number. Each IC schematic circuit symbol has a three or four character label that describes the column and row where pin 1 of that IC is located. The Detailed Circuit Description that follows refers to the ICs by this location label. For example, a 74LS640 IC whose 1 pin is located in Column T and row 23 is referred to as T23. When reference is made to a schematic circuit symbol of a multiple section device, the symbol ID is used, followed by a hyphen and the letter designator. The symbol ID alone refers to single section ICs.

#### **Logic Conventions**

Logic signal names are indicated by all uppercase letters and numbers (i.e., OBS). A logic signal name that ends with a trailing slash represents an active low signal (i.e., INIT/).

There are several conventions that can describe the state of a logic signal. Some of these conventions are true or false, high or low, one or zero, and active or inactive. In the remaining METEOSAT discussion, all logic states are described with "high" and "low." This convention best describes the physical condition of a logic signal and is better suited for troubleshooting.

## Frame Sync Interface Section

The Frame Sync Interface is shown on sheet 1 of the schematics. It includes:

- Byte Selector

- Frame Sync Interface Controller

- ID Clock Pulse Inhibitor

#### **Byte Selector**