Space Stenc UWSSEC Publication No. 92.06.M2

# McIDAS

Man computer Interactive Data Access System

# SDA Hardware Manual

Issued June 1992

Copyright © 1992, Space Science and Engineering Center

Revised 1992

Space Science and Engineering Center University of Wisconsin - Madison 1225 West Dayton Street Madison, WI 53706 Telephone 608-262-2455 TWX 608-263-6738

## **Preface**

The SSEC Display Adapter is a plug-in printed circuit board developed by the University of Wisconsin's Space Science and Engineering Center (SSEC) that allows an IBM® PS/2™ \* desktop computer to function as a McIDAS (Man computer Interactive Data Access System) workstation. The workstation is the component of the McIDAS that provides the animated display of satellite imagery and weather data.

The SSEC Display Adapter (hereafter called "SDA") Workstation consists of off-the-shelf units and the SDA. This manual was prepared by SSEC to aid technicians in diagnosing hardware failures on the SDA to the component level. Hardware documentation for the off-the-shelf units is provided by the respective manufacturers.

The theory of operation in this manual is organized in these three increasing levels of detail:

- System Overview

- Functional Description

- Detailed Circuit Description

This three-tier approach allows all users (technicians, managers, etc.) to progress through this manual to the technical level of detail desired. That is, systems managers may use only the first or second level of detail to assist in making workstation-related decisions, while technicians may use all levels of detail.

<sup>\*</sup> IBM® is a registered trademark of International Business Machines Corporation.

PS/2<sup>™</sup> is a trademark of International Business Machines Corporation.

# **McIDAS SSEC Display Adapter**

| SDA Workstation Overview            | . 1  |

|-------------------------------------|------|

| McIDAS System Description           | . 1  |

| Satellite Data Antennas             | . 1  |

| Frame and Bit Synchronizers         | . 3  |

| Archive/Playbacks                   | . 3  |

| Multisourcerer                      | . 3  |

| Ingestors                           | . 3  |

| IBM Mainframe Computer              | . 4  |

| Disk Storage                        |      |

| Local Area Networks                 |      |

| Remote Communications Controller    |      |

| Protocol Converter                  | . 5  |

| Tape Drives                         |      |

| Workstation                         | . 5  |

| McIDAS SDA Workstation Components   | . 7  |

| IBM PS/2 Computer                   |      |

| Keyboard                            |      |

| Mouse                               |      |

| RAM Expansion Card                  |      |

| SDA                                 |      |

| LAN Adapter                         |      |

| Color Monitors                      |      |

|                                     | . 10 |

| SDA Card Functional Description     | . 11 |

| PS/2 Interface                      |      |

| Micro Channel Interface             |      |

| Data Bus Transceiver                |      |

| Dynamic RAM                         |      |

| Image Storage Requirements          |      |

| Graphics Storage Requirements       |      |

| Memory Partitioning                 |      |

| RAM Control                         |      |

| Video Output Section                |      |

| Digital to Analog Converters (DACs) |      |

| Interlace FIFO                      |      |

| Vertical Drive and Sync Drivers     |      |

| Interlaced Sync Driver              |      |

| SDA Outputs                         |      |

|                                     |      |

|                                     |      |

| U9 Functional Description           |      |

| U10 Functional Description          |      |

| Cursor Generator                    |      |

| Horizontal Start Offset             |      |

| Horizontal Half-Size                |      |

| Vertical Start Offset               |      |

| Vertical Half-Size and Type         | . 32 |

Revised 10/92

| Detailed Circuit Description          | <br> | <br> | <br> | <br>33 |

|---------------------------------------|------|------|------|--------|

| Schematic Conventions                 |      |      |      |        |

| Logic Conventions                     |      |      |      |        |

| PS/2 Interface                        |      |      |      |        |

| PALS U1 and U30 (22V10)               |      |      |      |        |

| Data Bus Transceiver (U2)             |      |      |      |        |

| Micro Channel Interface               |      |      |      |        |

| Board Bus and Transceiver Control     |      |      |      |        |

| XCVR                                  |      |      |      |        |

| POS Registers                         |      |      |      |        |

| Programmable Decoder                  |      |      |      |        |

| Chip Select Logic                     |      |      |      |        |

| Chip Select Feedback "OR"             |      |      |      |        |

| Unused Functions                      |      |      |      |        |

|                                       |      |      |      |        |

| Dynamic RAM (2M Byte)                 |      |      |      |        |

| Video Output Section                  |      |      |      |        |

| RAMDACs                               |      |      |      |        |

| Interlace FIFO                        |      |      |      |        |

| Output Drivers                        |      |      |      |        |

| Master Controller                     |      |      |      |        |

| U9 Detailed Circuit Description       |      |      |      |        |

| Memory Write Latch Strobe Generator   |      |      |      |        |

| Data Bus Interface                    |      |      |      |        |

| Graphics Mask and High/Low Word Sele  |      |      |      |        |

| Graphics Prioritizer and Processor    |      |      |      |        |

| One-of-Eight Selector                 |      |      |      |        |

| Resynchronizing Latch                 |      |      |      |        |

| Graphics Demultiplexer                |      |      |      |        |

| Command Latch                         | <br> | <br> | <br> |        |

| RAM Timing Generator                  | <br> | <br> | <br> | <br>53 |

| U10 Detailed Circuit Description      | <br> | <br> | <br> | <br>57 |

| Timing Generator                      | <br> | <br> | <br> | <br>57 |

| Address Strobe Generator              | <br> | <br> | <br> | <br>57 |

| RAM Read/Write Addressing Section .   | <br> | <br> | <br> | <br>58 |

| Address Input Latch                   |      |      |      | 67     |

| RAMDAC Byte Selector                  | <br> | <br> | <br> |        |

| Interlace Generator                   |      |      |      |        |

| Interlaced Graphics Bus Demultiplexer |      |      |      |        |

| Interrupt Logic Block                 |      |      |      |        |

| Cursor Generator                      |      |      |      |        |

|                                       | <br> | <br> | <br> | <br>00 |

| SDA Diagnostics                       | <br> | <br> |      | 69     |

| High Level Diagnostics                |      |      |      |        |

| Installing the Diagnostics            |      |      |      |        |

| Running the Diagnostics               |      |      |      |        |

| Deleting the Diagnostics Menus        |      |      |      |        |

| Low Level Diagnostics                 |      |      |      |        |

| Installing the Diagnostics            |      |      |      |        |

| Running the Diagnostics               |      |      |      |        |

| Deleting the Diagnostics              |      |      |      |        |

| Determing the Diagnostics             | <br> | <br> | <br> | <br>OU |

| Supplemental Data                      |     |      |          |     |   | <br>   |    |      |   |       |  | 81    |

|----------------------------------------|-----|------|----------|-----|---|--------|----|------|---|-------|--|-------|

| PAL Equation Listings                  |     |      |          |     |   |        |    |      |   |       |  | 81    |

| Symbols and Abbreviations              |     |      |          |     |   |        |    |      |   |       |  | 82    |

| P22V10 Located at U1                   |     |      |          |     |   |        |    |      |   |       |  | 83    |

| P22V10 Located at U30                  |     |      |          |     |   |        |    |      |   |       |  | 85    |

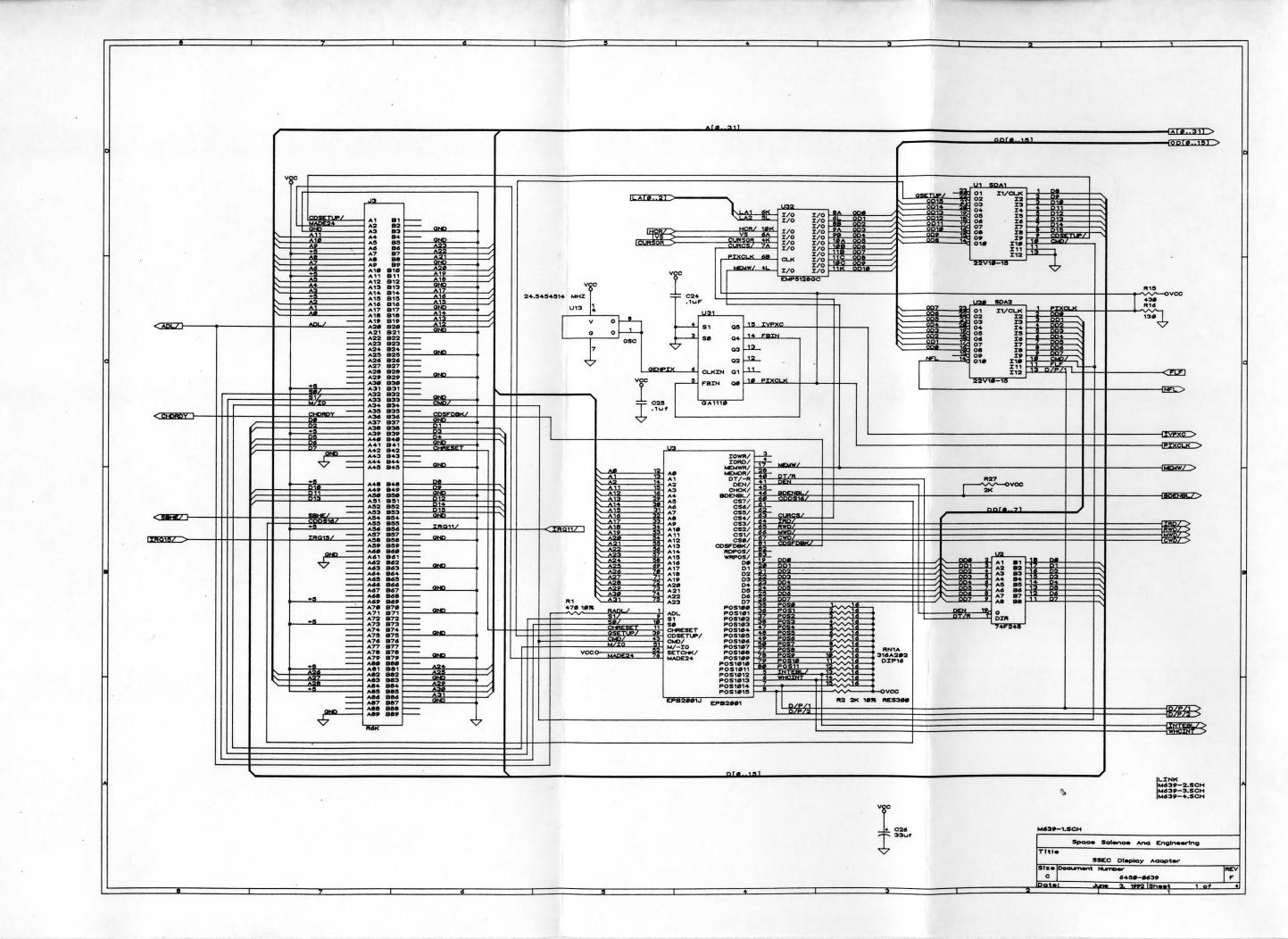

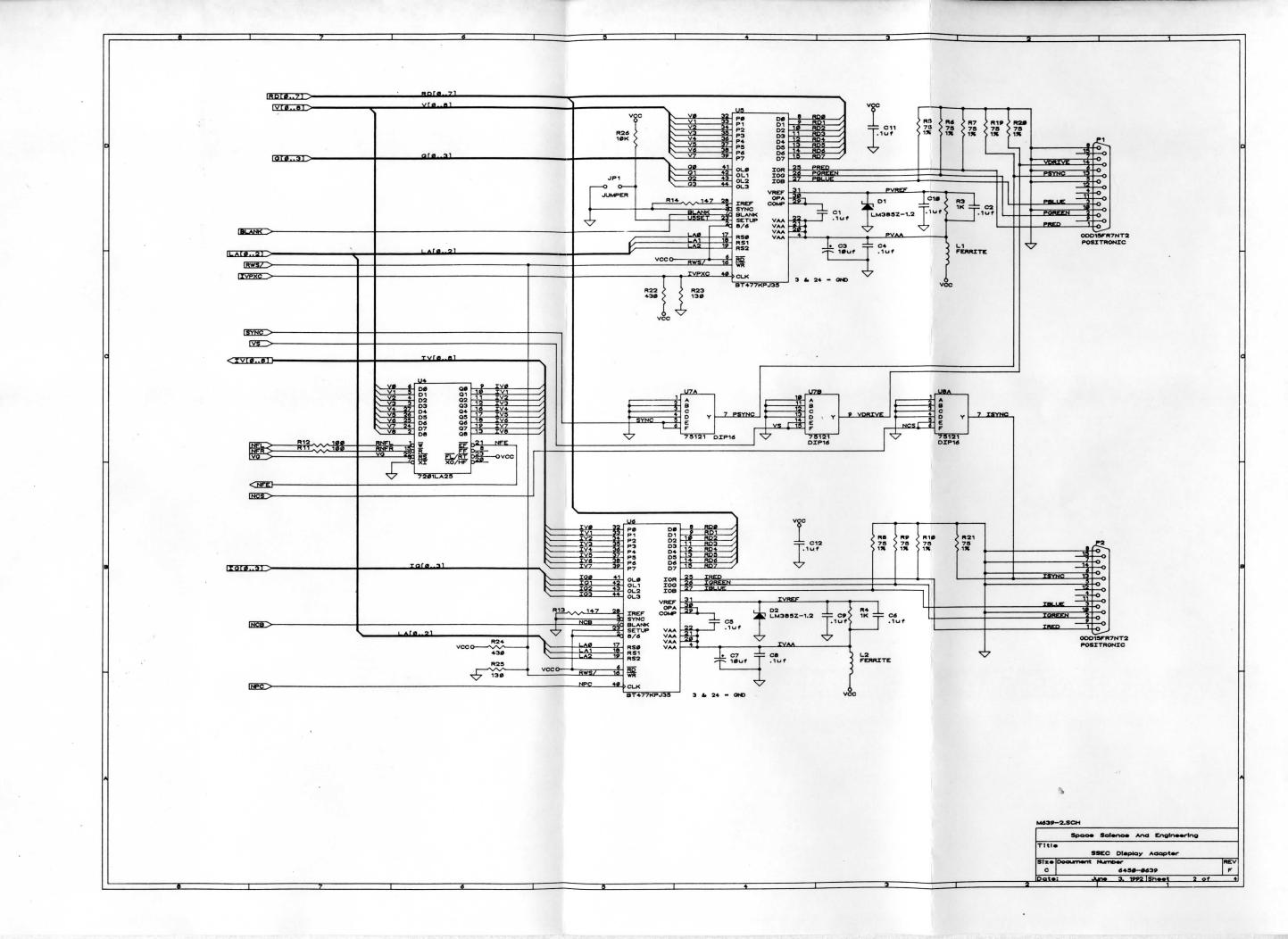

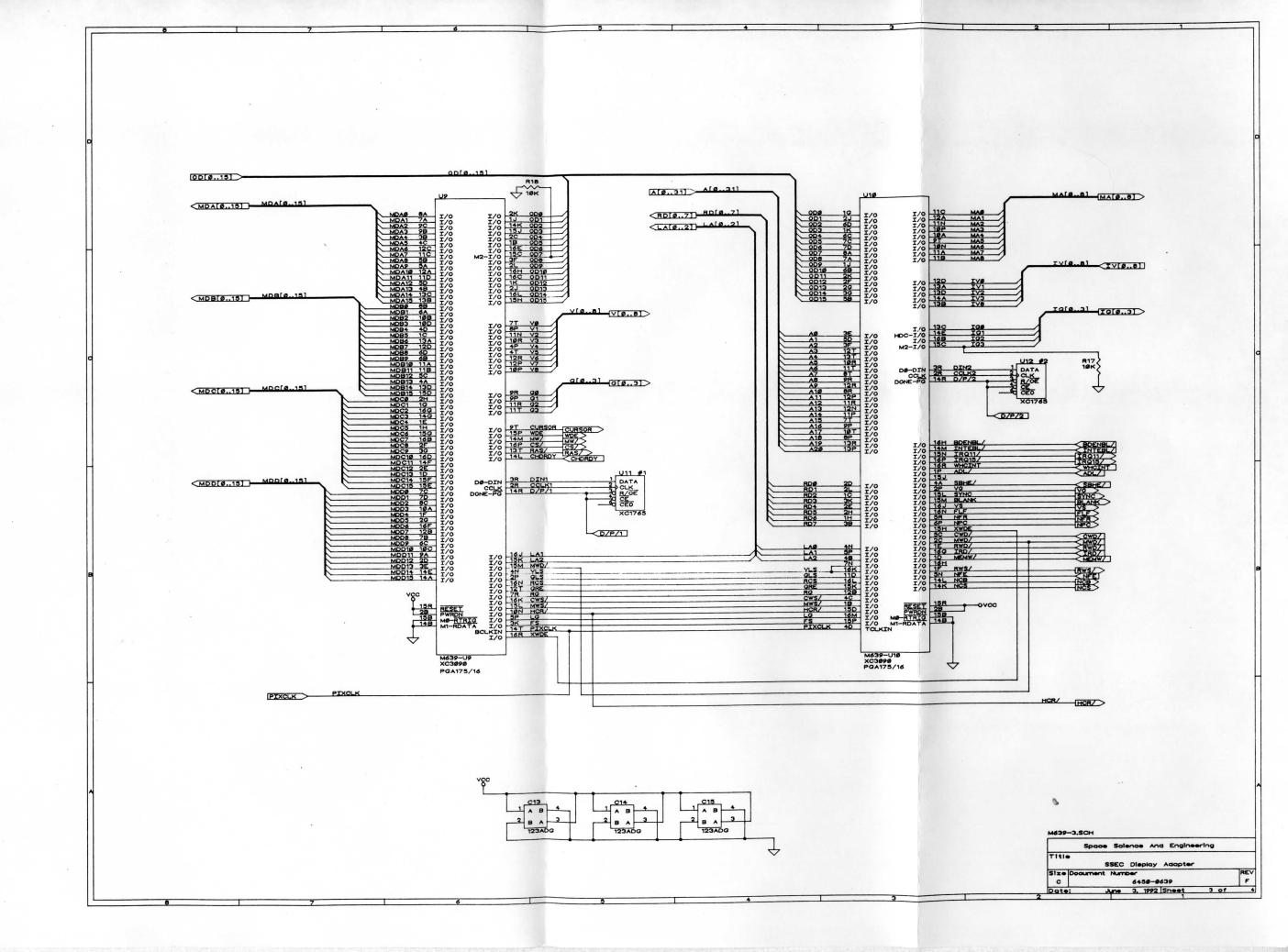

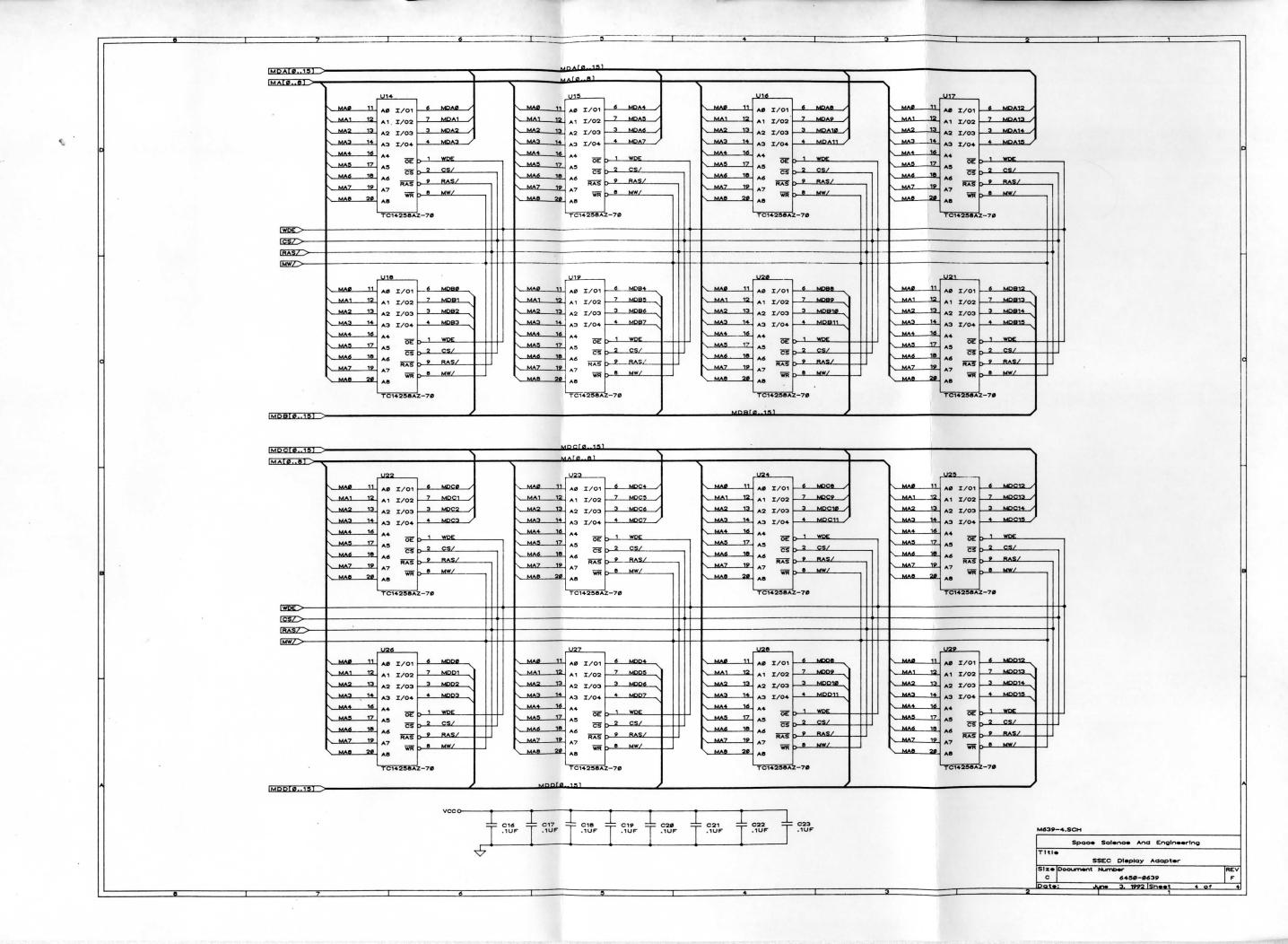

| Schematic Drawings 1 - 4               |     |      |          |     |   |        |    |      |   |       |  |       |

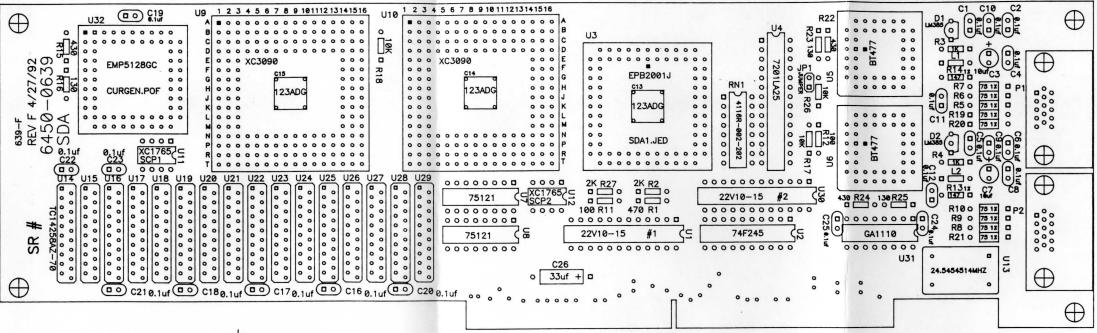

| Assembly Drawing 1                     |     |      |          |     |   |        |    |      |   |       |  |       |

| Appendix A                             |     |      |          |     |   |        |    |      |   |       |  |       |

| PS/2 Architecture                      |     |      |          |     |   | <br>   |    | . 10 |   |       |  | A-1   |

| Micro Channel Characteristics          |     |      |          |     |   |        |    |      |   |       |  | A-1   |

| Appendix B                             |     |      |          |     |   |        |    |      |   |       |  | ) els |

| Video Scan Timing Characteristics      |     |      |          |     |   | <br>   |    |      |   |       |  | B-1   |

| Interlaced Timing Characteristics      |     |      |          |     |   |        |    |      |   |       |  | B-1   |

| Progressive Scan Timing Characteristic | s . | • .• |          |     |   | <br>   |    |      |   |       |  | B-2   |

| Appendix C                             |     |      |          |     |   |        |    |      |   |       |  |       |

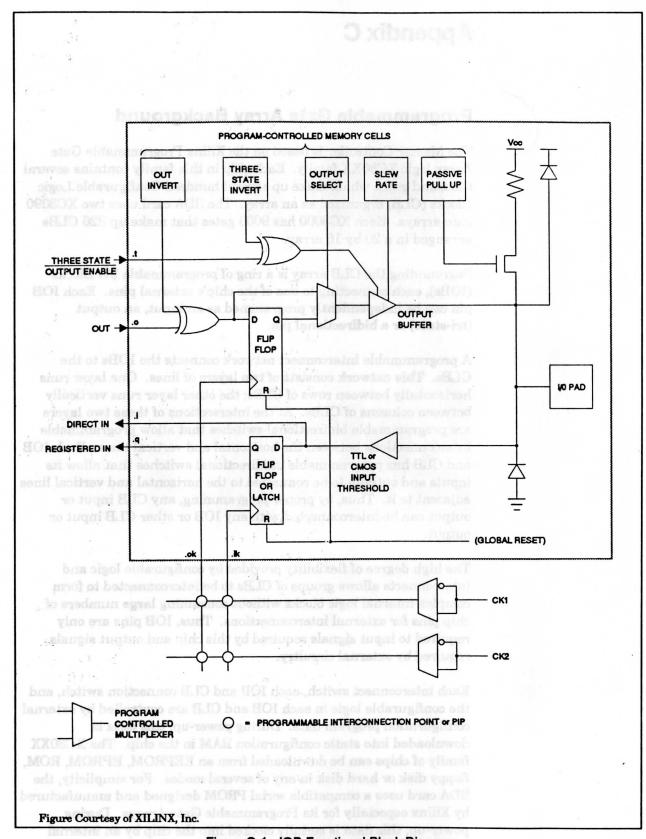

| Programmable Gate Array Background .   |     |      |          |     |   | <br>   |    |      |   |       |  | C-1   |

| Input/Output Block (IOB)               |     |      |          |     |   | <br>   |    |      |   |       |  | C-3   |

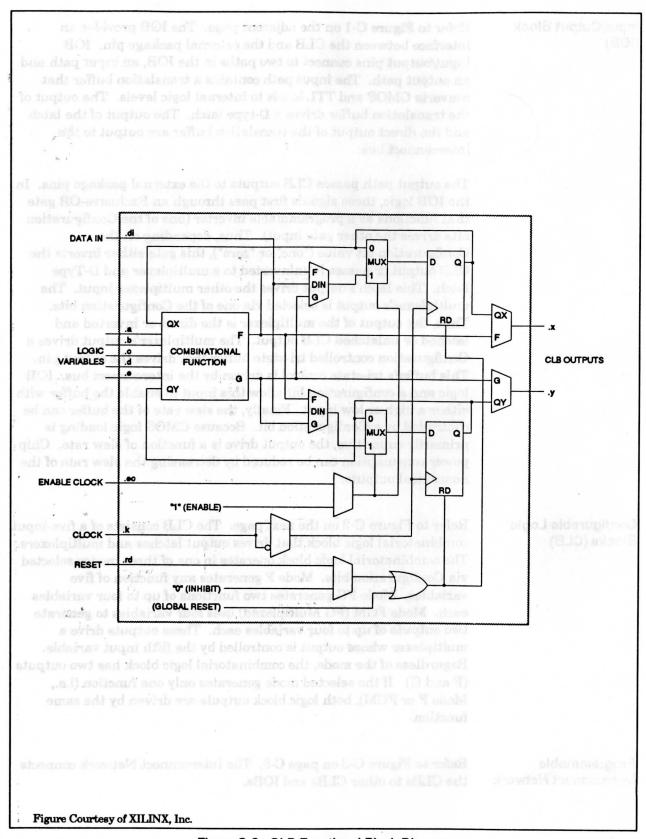

| Configurable Logic Blocks (CLB)        |     |      |          |     |   |        |    |      |   |       |  | C-3   |

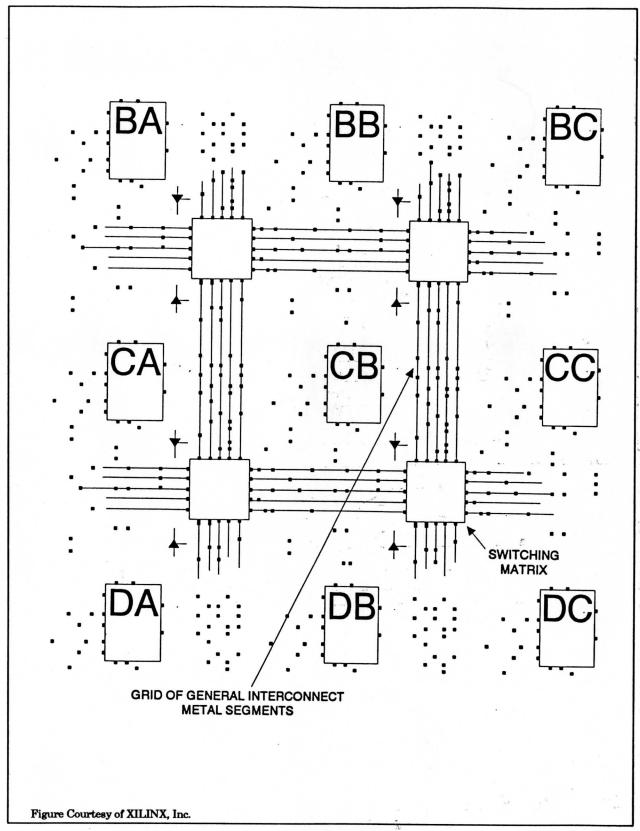

| Programmable Interconnect Network      |     |      |          |     |   | <br>٠. | ٠. |      | ١ | <br>٠ |  | C-3   |

| Appendix D                             |     |      |          |     |   |        |    |      |   |       |  |       |

| PS/2 Micro Channel Control Signals     |     |      |          |     |   |        |    |      |   |       |  | D-1   |

| ADL/(Address Decode Latch)             |     |      |          |     |   | <br>   |    |      |   |       |  | D-1   |

| CDDS16/ (Card Data Size 16)            |     |      |          |     |   | <br>   |    |      |   |       |  | D-1   |

| SBHE/(System Byte High Enable)         |     |      |          |     |   | <br>   |    |      |   |       |  | D-1   |

| MADE24 (Memory Address Enable 24)      |     |      |          |     |   | <br>   |    |      |   |       |  | D-2   |

| M/IO (Memory/Input Output)             |     |      |          |     |   | <br>   |    |      |   |       |  | D-2   |

| S0/ and S1/(Status bits 0 and 1)       |     |      |          |     |   | <br>   |    |      |   |       |  | D-2   |

| CMD/(Command)                          |     |      |          |     |   | <br>   |    |      |   |       |  | D-2   |

| CDSFDBK/(Card Selected Feedback)       |     |      |          |     |   | <br>   |    |      |   |       |  | D-2   |

| IRQ15/(Interrupt Request 15)           |     |      |          |     |   |        |    |      |   |       |  | D-3   |

| CDSETUP/(Card Setup)                   |     |      |          |     |   | <br>   |    |      |   |       |  | D-3   |

| CHRESET (Channel Reset)                |     |      |          |     |   |        |    |      |   |       |  | D-3   |

|                                        |     |      |          |     |   |        |    |      |   |       |  |       |

|                                        |     |      |          |     |   |        |    |      |   |       |  |       |

| Figures Tables and Timing              | Dia | ~    | <b>'</b> | ~   |   |        |    |      |   |       |  |       |

| Figures, Tables and Timing             | Dia | gı   | aı       | 113 | > |        |    |      |   |       |  |       |

| Figures                                |     |      |          |     |   |        |    |      |   |       |  |       |

| Figure 1. Simplified SSEC McIDAS       |     |      |          |     |   | <br>   |    |      |   |       |  | 2     |

| Figure 2. SDA Workstation              |     |      |          |     |   |        |    |      |   |       |  | 6     |

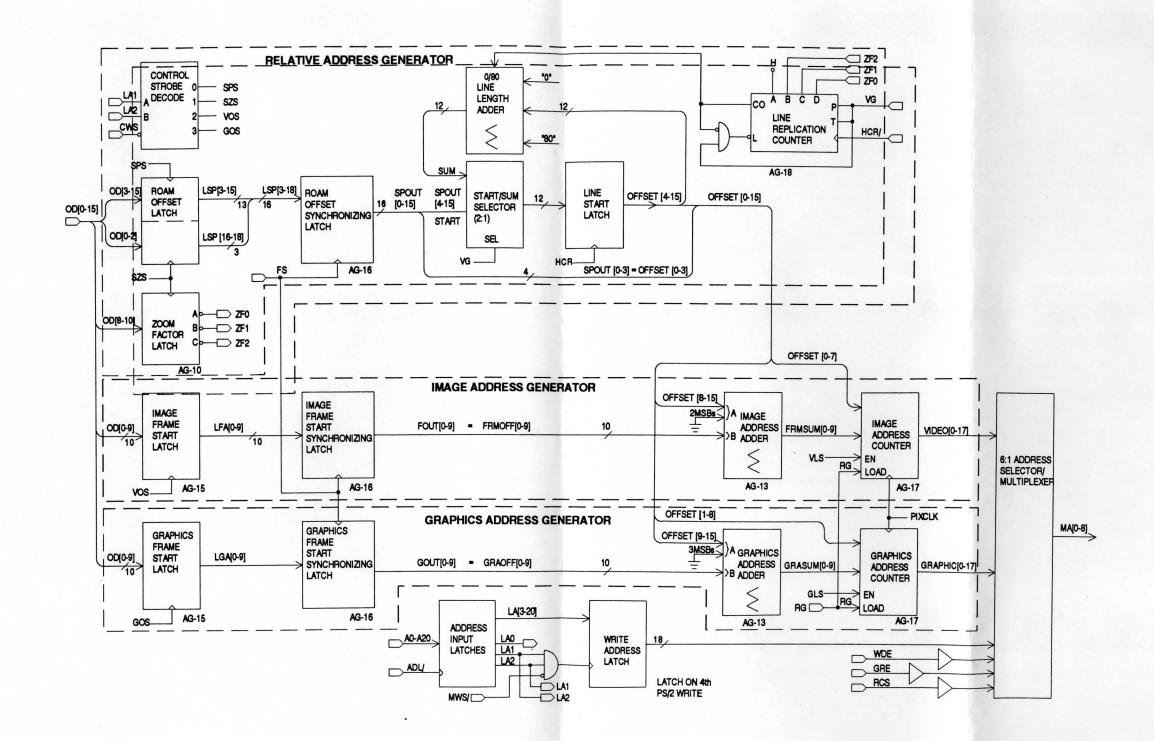

| Figure 3. SDA Functional Block Diagram |     |      |          |     |   |        |    |      |   |       |  | 13    |

| Figure 4. U9 Functional Block Diagram  |     |      |          |     |   |        |    |      |   |       |  | 22    |

| Figure 5. U10 Functional Block Diagram |     |      |          |     |   |        |    |      |   |       |  | 26    |

Revised 10/92

| Figure 6. EPB2001 Functional Block Diagram      | 36        |

|-------------------------------------------------|-----------|

|                                                 | 47        |

|                                                 | 54        |

| Figure 9. RAM Read/Write Addressing Section     | 63        |

| Figure C-1. IOB Functional Block Diagram        | C-2       |

|                                                 | C-4       |

|                                                 | C-5       |

| Tables                                          |           |

| Table 1. Typical Frame Mix RAM Address Space    | 16        |

|                                                 | 18        |

|                                                 | 28        |

|                                                 | 31        |

|                                                 | 32        |

|                                                 | 39        |

|                                                 | 42        |

|                                                 | 43        |

|                                                 | 46        |

|                                                 | 50        |

|                                                 | 51        |

|                                                 | <b>52</b> |

| Table 13. Zoom Factor Versus Area Magnification | 61        |

|                                                 | 69        |

|                                                 | 70        |

| Table 16. SDA High Level Diagnostics Tests      | 72        |

| Table A-1. Micro Channel Data Transfers         | A-2       |

|                                                 | D-2       |

|                                                 |           |

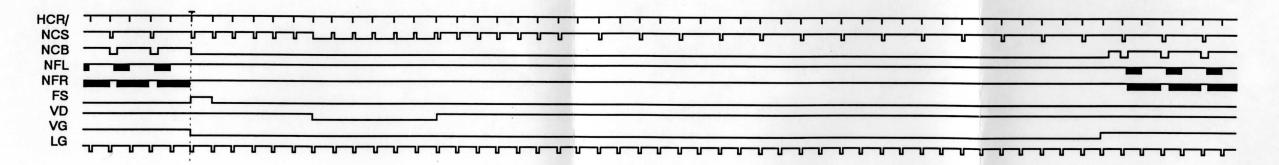

| Timing Diagrams                                 |           |

| Timing Diagram 1. RAM Timing (No Frame Load)    | 55        |

|                                                 | 55        |

| Timing Diagram 3. Progressive Scan Timing       | 59        |

|                                                 | 59        |

## Installing the SDA Board

The SDA (SSEC Display Adapter) board installation requires:

- · one SDA board

- one diskette labeled SDA Diagnostics, version 1.1

The SDA Diagnostics diskette contains the SDA High Level and Low Level diagnostics software and the SDA Adapter Description File (ADF).

Use the steps below to install the SDA software and board.

- Turn off the computer and open the top cover. Insert the SDA board into any unused 32-bit Microchannel Adapter (MCA) slot in your IBM PS/2. Handle the card by its edges, trying not to touch parts or the edge connector.

- 2. Replace the top cover on the PS/2. Connect the video cable from the VGA monitor to the top plug on the SDA.

- 3. Insert your Backup Copy of the Reference diskette (not the Option diskette) and turn on the computer. Following the memory check, a 165 error is displayed on the screen, indicating an adapter was added or removed. The system will boot with the Backup Copy of the Reference diskette.

- 4. To continue,

Press: Enter

When the system asks if you want to automatically configure the system,

Press: N

You must choose this option, as the Adapter Description File (ADF) is not yet present on your Backup Copy of the Reference diskette.

Revised 10/92

5. When the Main Menu is displayed,

Select: 4 (Copy an Option Diskette)

Remove the Backup Copy of the Reference diskette and insert the SSEC supplied SDA Diagnostics diskette that contains the SDA ADF file. This diskette is located in the inside front cover pocket of this manual.

When prompted, remove the SDA Diagnostics diskette and insert the Backup Copy of the Reference diskette. Then,

Press: Enter

to copy the ADF file to the Backup Copy of the Reference diskette.

7. When the Main Menu is displayed,

Select: 2 (Set Configuration)

8. When the Set Configuration Menu is displayed,

Select: 2 (Run Automatic Configuration)

9. To exit.

Press: F3

Remove the Backup Copy of the Reference diskette. Then,

Press: Enter

The system boots with the new hardware configuration and completes the installation of the SDA board.

10. Change to the \MCIDAS\TOOLS directory and run the SETUP program to configure McIDAS. See page 1-11 of the McIDAS-OS2 Users Guide for more information on SETUP.

## **SDA Workstation Overview**

The McIDAS SSEC Display Adapter Workstation is the link between the user and McIDAS. It provides the animated display of satellite imagery and weather data. The workstation allows the user to issue commands to the McIDAS mainframe and receive digital image and graphics information from it. The SDA Workstation stores and processes image and graphics data and displays this data on one or more color monitors. Users' systems range from a single McIDAS workstation linked remotely to SSEC's McIDAS, to complete systems like SSEC's McIDAS, to more elaborate systems similar to SSEC's McIDAS but with more or different components.

This overview provides:

- a brief description of SSEC's McIDAS to show how the SDA Workstation fits into the total system

- a description of the components that make up a complete SDA Workstation

## **McIDAS System Description**

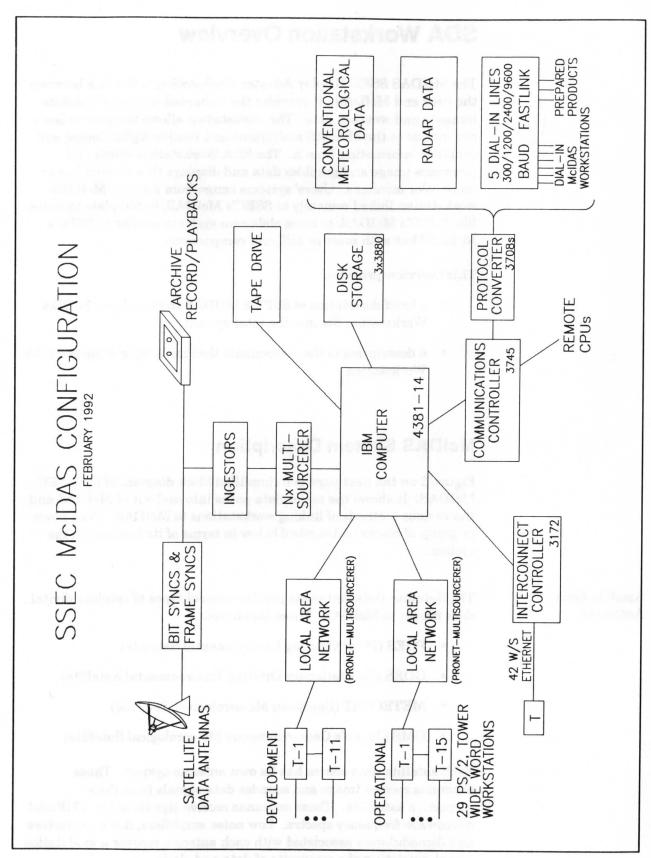

Figure 1 on the next page is a simplified block diagram of the SSEC McIDAS. It shows the major data paths into and out of McIDAS and the various methods of linking workstations to McIDAS. Each block or group of blocks is described below in terms of its function in the system.

## Satellite Data Antennas

The Satellite Data Antennas provide several types of satellite digital data inputs to McIDAS. These inputs are:

- POES (Polar Orbiting Environmental Satellite)

- GOES (Geostationary Orbiting Environmental Satellite)

- METEOSAT (European Meteorological Satellite)

- GMS (Japan's Geosynchronous Meteorological Satellite)

Each satellite data source has its own antenna system. These antennas receive image and sounder data signals from their respective satellites. These antennas receive signals in the VHF and microwave frequency spectra. Low noise amplifiers, down converters and demodulators associated with each antenna recover a modulation signal consisting of a composite of data and clock.

Figure 1. Simplified SSEC McIDAS

## Frame and Bit Synchronizers

Each demodulated signal is processed by a Bit Synchronizer (Bit Sync) which separates the signal into a serial data stream and clock signal. The Bit Syncs send their outputs to a respective Frame Synchronizer (Frame Sync) which outputs a serial or parallel data format (depending on the signal type - POES, GOES, METEOSAT, etc.) to the Archive/Playbacks and Ingestors.

## Archive/Playbacks

The Frame Syncs' outputs are stored digitally on video cassette cartridges. The playback unit allows previously recorded satellite data to be read into the system at any time for user analysis.

#### Multisourcerer

IBM mainframe inputs and outputs are via the mainframe's I/O channels. The Multisourcerer is an SSEC designed and built programmable interface between an IBM I/O Channel and up to six external devices (ingestors, etc.). It contains a card cage with an interface controller and six unused Multibus compatible board slots. The following Multisourcerer applications cards are available:

- ingestors

- · Local Area Network (LAN) controllers

- · synchronous communications controllers

SSEC's McIDAS uses several Multisourcerers because of its complexity. However, a single Multisourcerer may control all three types of applications cards simultaneously in a less complex McIDAS.

### Ingestors

Each type of satellite has its own ingestor card. SSEC has developed ingestors for the following satellite systems:

- POES

- GOES Imaging

- GOES Sounding (2-card set)

- METEOSAT

- GMS (Japan's Geosynchronous Meteorological Satellite)

- GOES Mode AAA Auxiliary Block

Ingestors receive data, clock and control signals from their respective Frame Sync or Archive/Playback. Ingestors assemble incoming data into complete scans or blocks of data. Upon command from the mainframe, the ingestors send requested frames or blocks (or parts of frames or blocks) to the mainframe via the Multisourcerer's interface controller. The ingestors relieve the mainframe of much of the computing overhead associated with the ingest process.

## IBM Mainframe Computer

The IBM mainframe computer (4381-14) receives imagery data from the ingestors via their Multisourcerer, and radar and conventional meteorological data via the Communications Controller. The mainframe computer contains the operating system, applications programs and subroutines. It functions as a data processor, database management system and data analyzer.

## Disk Storage

Currently, SSEC's McIDAS has a storage capacity of approximately 33.8 gigabytes (33.8 billion bytes). The disk storage is divided into 6999 digital areas in which several databases reside. Three of the major databases are:

- · image files

- Meteorological Data (MD) files

- grid files

An image (area) file contains digitized satellite visual or infrared sensor data. An MD file is a generic file for single location observations (nonimage). It accommodates many types of data under one general structure. A grid file contains fields analyzed at regularly-spaced latitude and longitude locations (grids) from observational data.

#### Local Area Networks

Local Area Networks (LANs) link groups of workstations to the mainframe. Figure 1 shows these three LANs:

- Operational

- · Ethernet

- Development

These LANs provide high speed data transfers between the mainframe and workstations. No data is transferred between workstations though this is not a LAN limitation.

The Operational network is a ProNET<sup>™</sup> \* LAN manufactured by Proteon, Inc. The LAN is a two-card set that is plugged into a Multisourcerer. The Multisourcerer is an interface between the LAN cards, which control up to 15 McIDAS workstations, and the IBM computer channel.

<sup>\*</sup> ProNET<sup>™</sup> is a trademark of Proteon, Inc.

The Ethernet LAN is interfaced to the mainframe via the Interconnect Controller (IBM 3172). SSEC currently has about 42 workstations on the Ethernet LAN.

The Development LAN is similar to the Operational LAN (ProNET LAN). It is used to develop new hardware.

## Remote Communications Controller

The Remote Communications Controller is an interface between the IBM computer and:

- other McIDAS installations

- · the Protocol Converter

The Remote Communications Controller allows SSEC's McIDAS to exchange a variety of meteorological data. The Protocol Converter provides several additional types of data inputs and outputs.

#### **Protocol Converter**

The Protocol Converter links asynchronous dial-up workstations to the mainframe. It also provides radar and conventional meteorological data inputs to the mainframe. This conventional data, called point source data, is used to maintain the Meteorological (MD) database. Sources for conventional data include radiosondes, rocketsondes, ship reports, aircraft and radar.

## **Tape Drives**

The McIDAS operating system is periodically downloaded onto magnetic tape for upgrading other McIDAS installations.

## Workstation

The McIDAS workstation, which is designed for animated display of satellite imagery and weather data, has the following features:

- · real-time access to image and conventional data

- graphics overlays of images without image destruction

- animated displays of image or graphics frames at user selectable looping rates up to 15 frames/second

- pseudocoloring of imagery

- · user selected graphics colors

- · user defined hardware cursor

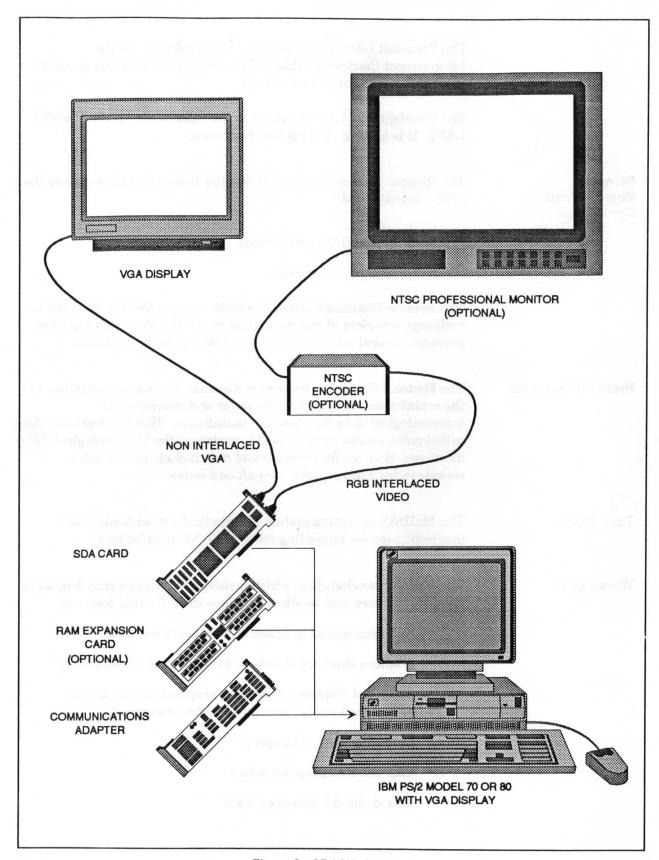

Figure 2. SDA Workstation

## **McIDAS SDA Workstation Components**

Figure 2 on the adjacent page shows the components that make up a complete SDA Workstation. Blocks containing "OPTIONAL" may be omitted in some workstations, with a corresponding reduction in workstation capability and flexibility.

The IBM PS/2 can be connected to the IBM host via a ProNET or Ethernet LAN link, or an asynchronous link (modem) to the host's Communications Controller. Regardless of the link type, there is a bidirectional data path between the IBM host and the PS/2.

The IBM PS/2 system provides the workstation intelligence and contains the following components:

- IBM PS/2 Model 70 or 80 computer

- keyboard

- mouse

- RAM Expansion Card

- SDA

- LAN Adapter

- color monitors (Zenith Model ZCM-1492 or equivalent)

Each of these components is described below.

#### IBM PS/2 Computer

Most SDA Workstation installations are based on the IBM PS/2 Model 70. The main difference between the Model 70 and 80 is the number of card adapter slots. The Model 70 has three adapter slots; the Model 80 has eight. Typically, the SDA, a LAN Adapter and, optionally, a Memory Expansion card are installed in the Model 70's three slots. The LAN Adapter provides the Model 70 with a LAN link to the host. The PS/2's built-in asynchronous serial port can be connected to a modem if an asynchronous link to the host is desired. A built-in parallel port can be used to drive an optional parallel line printer, and the RAM Expansion card provides up to eight megabytes of optional memory.

The PS/2 integrates the keyboard, mouse and color monitor into a user interactive workstation. The PS/2 relieves the host of some of its workload by performing many of the workstation related tasks at the workstation. This is in contrast to some of the older style non-PC based workstations.

## Keyboard

The keyboard is a standard keyboard supplied with the IBM PS/2 computer. The user interacts with McIDAS via the PS/2's keyboard to perform the following:

- request image and/or graphics frames from the host

- · establish display loops

- select zoom factors

- roam within an image

- position the cursor

- colorize images

- · define graphics colors

- · perform high and low level diagnostics

The keyboard is documented by its manufacturer.

#### Mouse

The mouse provides the PS/2 with cursor control. It is used to position the video cursor, roam within a frame and position the cursor (flashing underline symbol) during alphanumeric displays on the color monitor.

## RAM Expansion Card

The SDA Card contains sufficient on-board RAM to store up to six image frames. These frames can be displayed at animation looping rates of up to 15 images per second. If loop lengths greater than six images are required, additional images can be stored in PS/2 RAM. Because these additional frames must be downloaded into the SDA card to be displayed, the maximum looping rate decreases to six images per second (worst case). The RAM Expansion Card provides eight megabytes of additional memory.

SDA

The SDA is an IBM PS/2-compatible Micro Channel<sup>™</sup> \* adapter printed circuit board designed and built by SSEC. It performs all TV display functions. Specifically, it:

- converts the requested frame stored in its on-board memory as 64-bit digital words, to horizontal scan lines of analog video

- produces all necessary clocking and TV timing signals (horizontal and vertical sync plus blanking) required for displaying TV images

- · colorizes the images

- overlays up to four graphics planes on the image data

- outputs the analog data in progressive scan and interlaced RGB (Red, Green and Blue) formats

- allows the user to set the zoom factor, enable or disable graphics bit planes, load colorizer tables, roam within a selected image and select the image frame to be displayed

- generates a cursor in response to PS/2 commands

The progressive scan output is the standard output. However, the same data stream that drives the progressive scan output also drives an interlace converter that produces an interlaced RGB output for driving an optional NTSC Encoder. The NTSC Encoder produces a composite NTSC output for use in TV studios, etc., and driving the optional NTSC monitor. The interlace converter can be configured to generate the European TV format in lieu of the US TV format.

**LAN Adapter**

Workstations located within a few hundred feet of the host can be connected to the host via a Local Area Network (LAN). SSEC supports two LAN types, ProNET and Ethernet. Either LAN requires an access adapter for each network (workstation or host) member. The host's adapter resides in a Multisourcerer which links the LAN adapter to the IBM channel. The workstation's adapter resides in the PS/2. The LAN Adapter card shown in Figure 2 is specific to the LAN being used. If the LAN is ProNET, this card is a ProNET Adapter Model P1800. Since the OS/2 environment supports several sources of Ethernet adapter cards, the LAN Adapter can be one of several Ethernet Adapter Cards if the LAN is Ethernet.

Micro Channel<sup>™</sup> is a trademark of International Business Machines Corporation

#### **Color Monitors**

The SDA Workstation uses two 14" Zenith Model ZCM-1492 color monitors or equivalent. One is used for PS/2 command and control functions; the other displays the image and graphics outputs of the SDA board. These monitors require 0.7V RMS red, green and blue drive signals, and composite sync from their respective drive sources. These monitors are non-interlaced and have horizontal and vertical scan frequencies of 31.5 KHz and 60 Hz, respectively. Other monitors meeting these specifications may be substituted.

If an optional NTSC monitor is used, it requires an NTSC encoder. This encoder is driven by the interlaced RGB and interlaced composite sync outputs of the SDA card.

## **SDA Card Functional Description**

The SDA Workstation is a collection of commercial devices and the SDA board. Documentation for the commercial devices is furnished by their respective manufacturers and is not repeated here. The SDA is documented in detail in this manual. The documentation consists of this Functional Description and a Detailed Circuit Description.

Much of the SDA control logic is contained in two Xilinx Programmable Gate Array chips. These chips contain the equivalent of 18,000 logic gates. Hundreds of pages of documentation could be dedicated to the functional description of these two chips without necessarily resulting in more efficient corrective maintenance. Since there are only four components in the control section, substitution of the suspected component with a known good component may be the most effective troubleshooting procedure. Therefore, documentation for these components provides sufficient functional information and timing diagrams to allow you to understand the interaction between the components in the control section and between the control section and the remaining SDA card sections. This should allow you to diagnose control section problems to one of the four chips.

It would be difficult, if not impossible, to understand the SDA board from a functional or circuit perspective without at least a cursory understanding of the PS/2 Micro Channel architecture. Appendix A provides basic information on the PS/2 architecture. For additional Micro Channel information, consult the manufacturer's documentation.

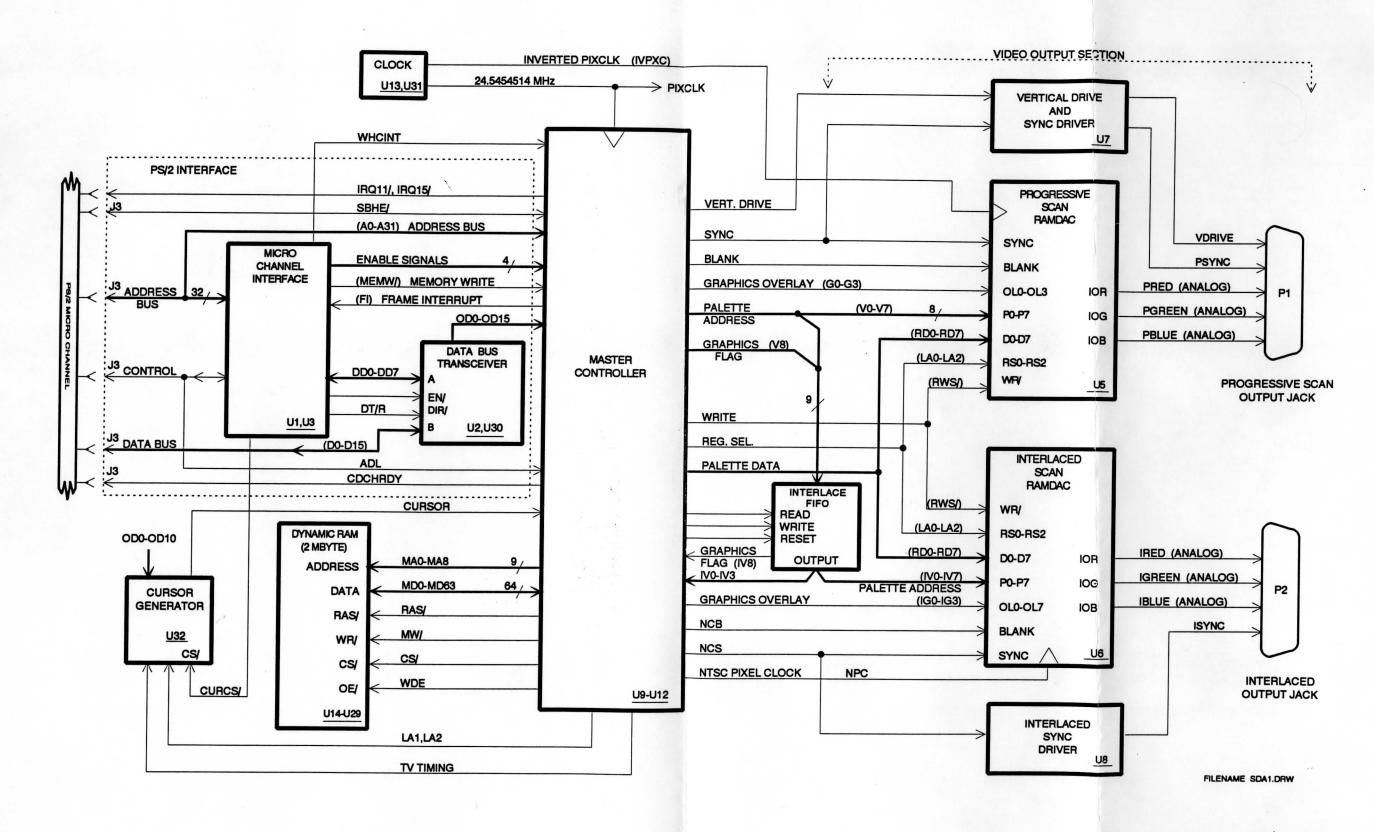

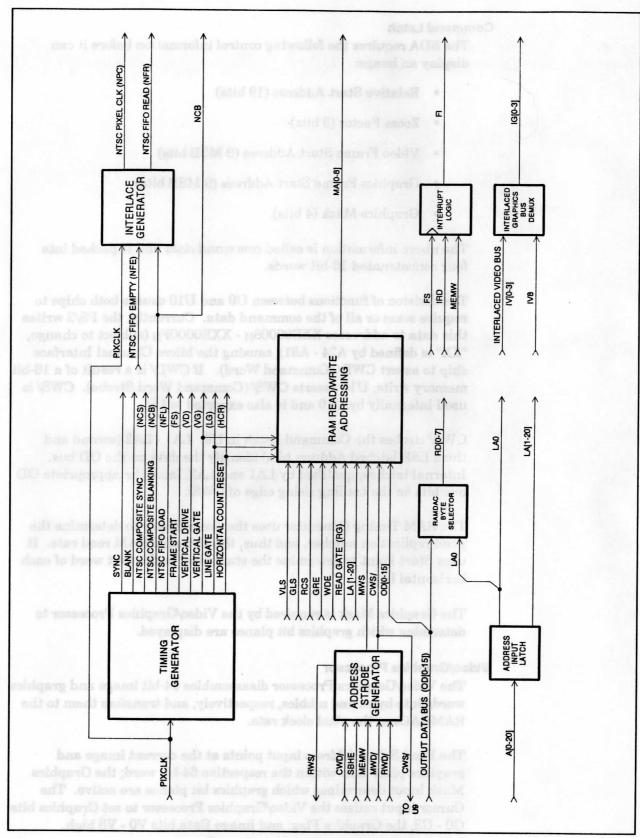

The SDA is built on an IBM PS/2 Micro Channel Adapter form factor board. Refer to Figure 3, the SDA Functional Block Diagram, on page 13. This board consists of a PS/2 Interface, two megabytes of dynamic RAM, a Video Output Section and a Master Controller. The extensive functionality designed into the SDA board is primarily the result of using two Programmable Gate Array chips for the Master Controller.

Issued 6/92

<sup>\*</sup>Xilinx<sup>™</sup> and Programmable Gate Array<sup>™</sup> are trademarks of Xilinx Incorporated.

## PS/2 Interface

The PS/2 Interface section makes the remainder of the SDA card appear as memory. This section consists of the Micro Channel Interface block and the Data Bus Transceiver.

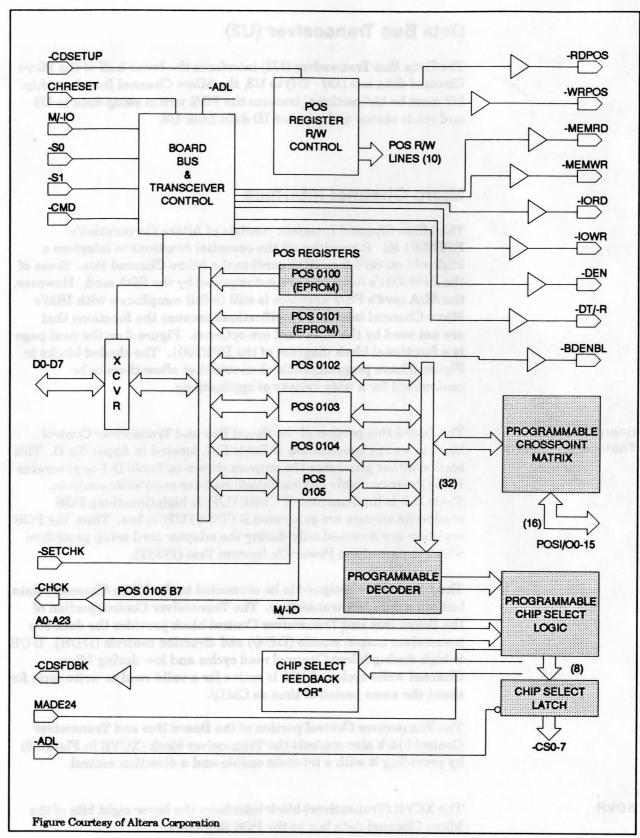

## Micro Channel Interface

The Micro Channel Interface consists of a programmable (EPROM) custom logic IC specifically designed and manufactured by the Altera Corporation to interface the IBM Micro Channel to a PS/2 add-on card (called *adapter* by IBM), i.e., the SDA.

Address lines A24 - A31 select the 16M byte memory block in which the SDA address space is located. Address lines A21 - A23 further specify a 4M byte address block within the 16M byte range. Thus, A21 - A31 specify the 4M byte address space within the 4G byte address capability of the PS/2. This allocation space information is stored in the Micro Channel Interface block. The PS/2 Interface section monitors the Micro Channel to determine if an address on the address bus is intended for the SDA card. When an SDA memory address is detected by the Micro Channel Interface block, it asserts one or more inputs to the Master Controller.

PS/2 addresses may be either memory or I/O type. The Micro Channel Interface uses the PS/2's cycle, and bus-cycle status input lines to determine whether the address is a memory read or write, or an I/O read or write. Only memory write operations are used by the SDA card. When a valid memory write address is detected, the PS/2 Interface asserts MEMW/. This signal functions as a write control signal for the Master Controller.

The SDA accepts display control data from the PS/2 and synchronizes it during the vertical blanking period. This prevents the PS/2 data from causing interference in the video display. The Master Controller asserts IRQ11/ or IRQ15/ (Interrupt Request) at the start of each progressive scan frame/field pair. The PS/2 uses the interrupt to drive the loop rate. Upon interrupt, the PS/2 sends video display control data to the SDA which it uses to display the next frame.

## Data Bus Transceiver

The Data Bus Transceiver interfaces the Micro Channel's data bus to the Micro Channel Interface and Master Controller blocks. This transceiver reduces the Micro Channel loading caused by these two blocks to one unit load. The transceiver passes PS/2 data inputs to the Micro Channel Interface and Master Controller blocks and passes POS (Programmable Option Select) register status from the Micro Channel Interface to the PS/2 (DD0 - DD7). Via the Master Controller, the PS/2 writes image and graphics data to the RAM and color enhancement data to the Video Output Section (OD0 - OD15). Currently, no data passes from the Master Controller to the PS/2.

Figure 3. SDA Functional Block Diagram

## Dynamic RAM (2M Bytes)

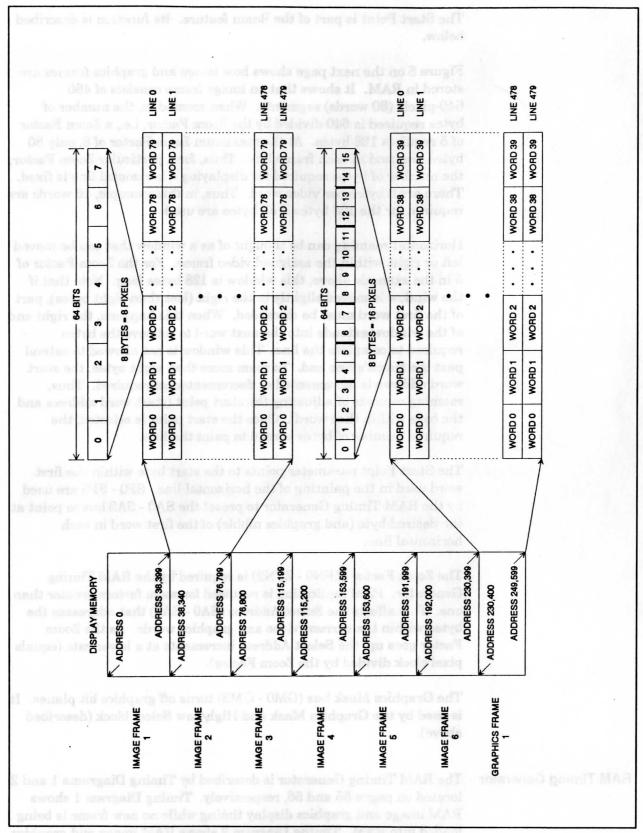

The SDA card contains a 2M byte dynamic RAM memory; actual storage capacity is 2,097,152 bytes. The memory is organized as 262,144 (40000<sub>H</sub>) 64-bit words (2M bytes). It stores the image and graphics frames.

## Image Storage Requirements

A McIDAS TV frame is defined as 480 horizontal lines of 640 pixels each. In the SDA Workstation, each image pixel is represented by 8 bits. Since each word contains 64 bits, they each represent 8 pixels. Therefore, a full resolution SDA Workstation horizontal line requires 80 words (80 words x 8 pixels = 640 pixels). A full resolution TV frame requires 38,400 words, (80 words/line x 480 lines = 38,400 words). This is the storage requirement for each stored image frame.

# Graphics Storage Requirements

Graphics frames require one-half as much storage as image frames because only four bits are used for each pixel. Thus, four graphics planes are available (each bit represents a graphics plane). Each graphics byte represents two graphics pixels; each 64-bit RAM word represents 16 graphics pixels. Each graphics frame requires 19,200 64-bit RAM words.

## **Memory Partitioning**

The RAM is arbitrarily partitioned into a mix of image and graphics frames. The image and graphics frame size is fixed at 38,400 and 19,200 words, respectively. Typically, there are six image frames and one graphics frame. Thus, 249,600 RAM words are used  $(6 \times 38,400)$  plus  $1 \times 19,200 = 249,600$ . If additional graphics frames are desired, two additional graphics frames are available for each image frame sacrificed. Thus, there can be as many as 13 graphics frames if no image frames are needed. Regardless of the mix, the memory always contains 249,600 active words and 12,544 unused words.

The graphics frame(s) can be physically located before, between or after the image frames. Thus, for the typical mix (six image frames and one graphics frame), there are seven possible start addresses for the graphics frame and two possible start addresses for each image frame. Table 1 on the next page shows the possible start addresses.

| Image<br>Frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Image Space if Graphics<br>Start Address is Above | Image Space if Graphics<br>Start Address is Below |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------------|

| dmanyb o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Image Start Address                               | Image Start Address                               |

| 1 od V as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0 - 38,399                                        | 19,200 - 57,599 *                                 |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 38,400 - 76,799                                   | 57,600 - 95,999                                   |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 76,800 - 115,199                                  | 96,000 - 134,399                                  |

| 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 115,200 - 153,599                                 | 134,400 - 172,799                                 |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 153,600 - 191,999                                 | 172,800 - 211,199                                 |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 192,000 - 230,399 **                              | 211,200 - 249,599                                 |

| * Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ics are located at 0 - 19,199                     |                                                   |

| the state of the s | nics are located at 230,400 - 24                  | 9,599                                             |

Table 1. Typical Frame Mix RAM Address Space

#### **RAM Control**

The Dynamic RAM consists of sixteen 262,144-word by 4-bit dynamic RAM chips connected to form a 262,144-word by 64-bit memory. Each RAM chip contains the following inputs/outputs:

- RAS/ (Row Address Strobe)

- CS/ (Chip Select)

- OE/ (Output Enable)

- WR/ (Write)

- A0-A8 (Address bits 0-8)

- I/O1-I/O3 (Input/Output data bits 0-3)

Except for the data pins, the corresponding pins of all chips are connected in parallel. The data pins are separate. Thus, there is one RAS/input, one CS/input, one OE/input, one WR/input, a 9-bit address input and a 64-bit data input/output port.

Internally, each chip is organized as a 512 by 512 by 4-bit array. These chips require a 9-bit row address and a 9-bit column address to address the array. The Master Controller places the row address (least significant 9 bits of the 18-bit address) on the address bus and strobes RAS/ to latch these bits into the RAM chips. Then, it places the column address on the address bus and strobes CS/ and OE/ (read) or WR/ (write).

The Dynamic RAM requires periodic refresh cycles to maintain data integrity. The memory's chips must receive refresh cycles at a minimum rate of 512 refreshes per 8 milliseconds. The refresh cycles are part of the display data retrieval cycle. This cycle is 16 pixel periods in length (approximately 640 nanoseconds). It consists of a graphics word fetch followed by an image word fetch followed by a write opportunity and concluded with another video word fetch. These four cycle phases are equal in duration (approximately 160 nanoseconds). A refresh cycle is executed during the write opportunity phase if there is no data to be written in the Dynamic RAM.

A horizontal line consists of 640 visible pixels and 140 blanked pixels. There are 40 potential refresh cycles during the visible portion. During horizontal blanking, only write opportunity cycles are executed, resulting in an additional 35 write opportunities. This results in about 75 potential refresh cycles per horizontal line. Since there are 255 horizontal lines per 8 milliseconds, there are about 19,125 refresh opportunities per 8 milliseconds or approximately 40 times the minimum refresh requirements (512 per 8 milliseconds). At maximum data throughput from the PS/2 to the SDA card, it's unlikely that half of the write opportunity cycles would be used for writing data into the Dynamic RAM. Under this condition, there would still be 20 times more refresh cycles than necessary.

## **Video Output Section**

The Video Output Section generates two RGB analog outputs from the 8-bit binary inputs. One output is a progressive scan format; the other is an interlaced format. Appendix B at the end of this manual provides a description of the differences and similarities between these two formats. The following description assumes you are familiar with the formats.

The SDA card uses the same video and graphics data to produce the interlaced and progressive scan drives. Comparing the two sets of timing characteristics in Table 2 below suggests a simple approach for converting the progressive scan drive to the interlaced format.

Issued 6/92 17

| Fiel<br>Fra | But All harm | H.Lines<br>Field | H.Scan<br>Time | V.Scan<br>Time | H.Blank       | V.Sweep              |

|-------------|--------------|------------------|----------------|----------------|---------------|----------------------|

| TV          | 2            | 262.5/<br>Field  | 63.55µs        | 59.94Hz        | 17%<br>H.Scan | 21/Field<br>42/Frame |

| PS*         | 1            | 525/<br>Frame    | 31.78µs        | 59.94Hz        | 17%<br>H.Scan | 42/Frame             |

Table 2. Progressive Scan and Interlaced (TV) Timing Comparisons

Table 2 suggests that buffering every other horizontal line of the progressive scan data and writing that data at one-half the progressive scan horizontal rate, will generate one TV field (262.5 even or odd lines) during a progressive scan frame. If this process is repeated during the next progressive scan frame, the other TV field is generated, completing the interlaced TV frame.

The SDA card currently outputs interlaced data in the RGB format. Since the RGB interlaced output meets the NTSC timing standards, it can be converted to the composite NTSC format using a standard external NTSC encoder. The SDA card can also be reconfigured to output RGB interlaced data in the PAL timing standards which can be converted to the composite PAL format using a standard external PAL encoder. PAL is the European interlaced TV standard.

# Digital to Analog Converters (DACs)

Each of the two DACs contains an integral video color palette RAM and a graphics overlay color palette RAM. This type of DAC is called RAMDAC<sup>M</sup> \* by its manufacturer, the Brooktree Corporation.

After the palettes are programmed via the PS/2 Interface and the Master Controller sections (RD bus in Figure 3), these RAMDACs use the 8-bit video input (P0 - P7 port in Figure 3) to internally address one of 256 24-bit video color palette RAM words. The 24-bit word consists of three bytes of magnitude data, one byte each for RED, GREEN and BLUE. The DAC simultaneously converts its three bytes of magnitude data to analog. Thus, the RAMDACs convert the 8-bit inputs to preassigned values of red, green and blue analog outputs.

<sup>\*</sup> RAMDAC<sup>™</sup> is a trademark of Brooktree Corporation.

The RAMDACs have a 4-bit graphics overlay color palette RAM addressing input (OL port - see Figure 3). If any bit in this input is high (on), the 256-word by 24-bit video color palette RAM is switched off and a 15-word by 24-bit graphics overlay color palette RAM is switched on.

The Cursor Generator (described later) asserts CURSOR whenever a the current pixel being painted is a cursor pixel. CURSOR is an input to the Master Controller which sets all four graphics bits high if CURSOR is asserted. Thus, if CURSOR is asserted, the Master Controller writes FH to the OL port. The 24-bit data stored in this overlay address determines the cursor's color. The Master Controller allows only these five graphics overlay addresses:

- 1H (graphics bit plane one lowest priority)

- 2<sub>H</sub> (graphics bit plane two)

- 4H (graphics bit plane three)

- 8<sub>H</sub> (graphics bit plane four)

- FH (cursor bit highest priority)

Thus, on a pixel-by-pixel basis, the cursor has priority over all other data, and graphics data has priority over image data. However, from the RAMDAC's perspective, the cursor is treated as graphics overlay data. Thus, any references to graphics in the Video Output Section descriptions also pertain to the cursor.

## Interlace FIFO

The Interlace FIFO in Figure 3 is a 9-bit by 512-word First-In First-Out buffer. It buffers every other progressive scan horizontal line. Eight-bit Input data is written at the pixel clock rate, but the data is read at one-half the pixel clock rate. Immediately after loading the 640th pixel of a progressive scan line, the FIFO contains 320 stored pixels. The other 320 pixels were read out during the unload process. Since only every other progressive scan is stored, the FIFO is emptied just prior to the start of the next used progressive scan. Data reading and writing are controlled by the Read and Write control signals generated by the Master Controller.

V0 - V7, the data inputs to the FIFO, are multiplexed video and graphics. The Graphics Flag, a Master Controller output, indicates whether the current data on the V0 - V7 bus is video or graphics data. If the current pixel data is graphics, only the lower four input bits carry valid data and the Graphics Flag bit is a one; if the current pixel data is video, all eight input bits are valid and the Graphics Flag bit is zero. The Graphics Flag is stored as the ninth bit in the FIFO.

The FIFO's eight output bits (IV0 - IV7) drive the P0 - P7 port on the RAMDAC. In addition, IV0 - IV3 are also sent to the Master Controller along with the output Graphics Flag (FIFO's ninth bit). If the output Graphics Flag is high, the Master Controller routes the IV0 - IV3 inputs to the IG0 - IG3 outputs, respectively. Thus, the Master Controller demultiplexes the graphics from the multiplexed V0 - V7 bus. When the output Graphics Flag is high, the V4 - V7 inputs and the IV4 - IV7 outputs are invalid because the lower four video bits were replaced by the graphics bits in the multiplexing process. This causes no problem, however, because the RAMDACs' entire video color palette RAM is switched off whenever any overlay bit input is high.

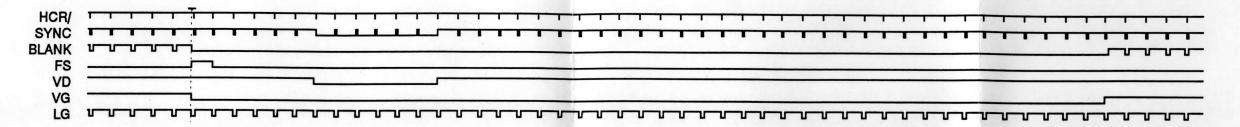

## Vertical Drive and Sync Drivers

The Sync Driver is driven by SYNC, the progressive scan composite sync output of the Master Controller. The Sync Driver provides the PSYNC (Progressive composite SYNC) output to P1, the Progressive Scan Jack. The Vertical Drive Driver provides the VDRIVE (Vertical DRIVE) output to P1. VDRIVE is required by some progressive scan monitors.

## Interlaced Sync Driver

Separate composite sync and blanking signals are generated for the Interlaced Scan RAMDAC. In addition, the Interlaced Sync Driver, driven by NCS (NTSC Composite Sync), provides composite interlaced sync (ISYNC) to the Interlaced Output Jack.

#### **SDA Outputs**

The interlaced RGB and sync outputs can be converted to a broadcast compatible composite signal by a suitable NTSC or PAL converter. The converter's composite output signal can drive an NTSC or PAL monitor, VCRs, TV broadcast transmitter equipment, etc. The progressive scan output drives a progressive scan monitor such as the Zenith Model ZCM-1492 color monitor.

unload process. Since only every other progressive scan is stored, the

data is video, all sight input bits are valid and the Grophics Plag bit is zero. The Grophics Plag is stored as the minth bit in the FIPO.

## **Master Controller**

The Master Control block in Figure 3 consists of four ICs that contain the equivalent of several thousand logic gates. This block:

- generates all display timing (sync, blanking, etc.)

- assembles 16-bit PS/2 words into 64-bit RAM words

- disassembles 64-bit RAM words into image bytes or graphics nibbles

- modifies image and graphics data read rates as a function of the zoom factor

- modifies the image and graphics start location as a function of roaming

- generates the Interlace FIFO read, write and reset strobes

- generates all RAMDAC control signals

- interfaces the OD data bus to the RAMDAC RD bus during RAMDAC programming and palette loading

- generates all RAM control signals and refresh cycles

- provides wait states, if necessary, during PS/2 to SDA RAM transfers

The Master Controller consists of two Programmable Gate Arrays. Appendix B in this manual provides a brief background on the Xilinx Programmable Gate Array technology to show its functional capabilities. For additional information on these devices, refer to the Programmable Gate Array Data Book by Xilinx Incorporated.

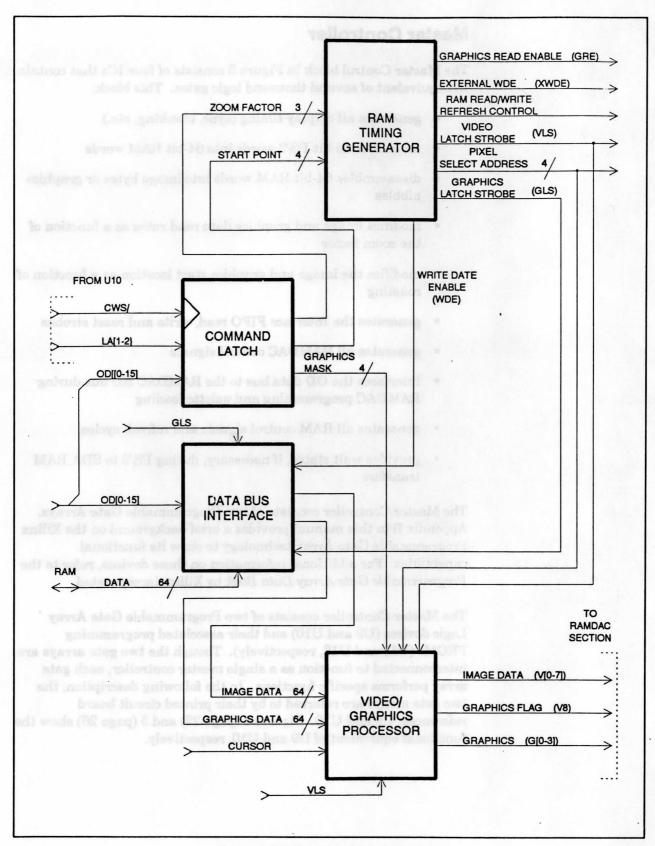

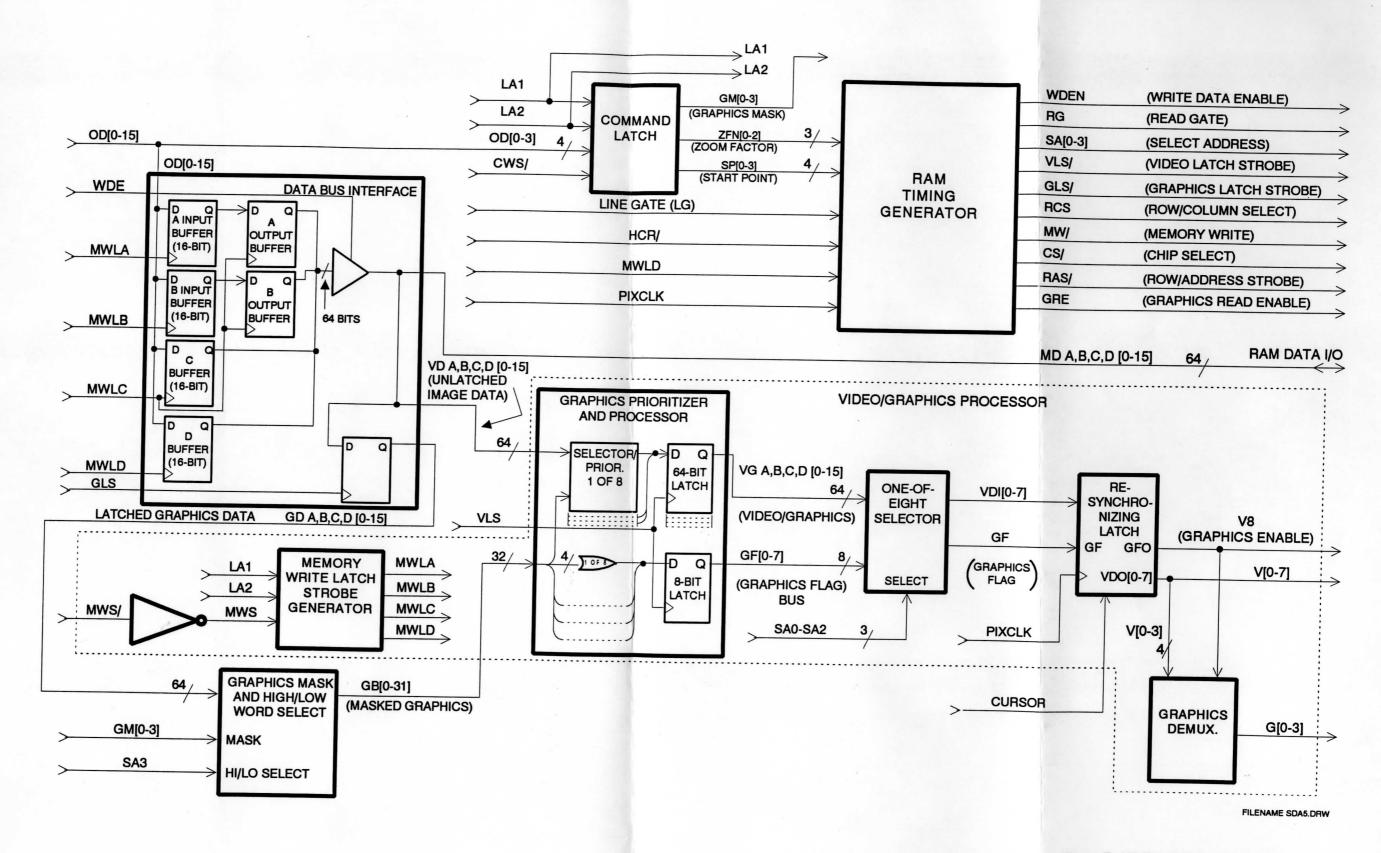

The Master Controller consists of two Programmable Gate Array Logic devices (U9 and U10) and their associated programming PROMs (U11 and U12, respectively). Though the two gate arrays are interconnected to function as a single master controller, each gate array performs specific functions. In the following description, the two gate arrays are referred to by their printed circuit board references, U9 and U10. Figures 4 (page 22) and 5 (page 26) show the functional equivalent of U9 and U10, respectively.

Issued 6/92 21

Figure 4. U9 Functional Block Diagram

## U9 Functional Description

Refer to Figure 4 on the adjacent page. U9 consists of these functional sections:

- Data Bus Interface

- RAM Timing Generator

- Command Latch

- · Video/Graphics Processor

## **Data Bus Interface**

The Data Bus Interface provides a data write path between the PS/2 and the Dynamic RAM, and a data read path between the Dynamic RAM and the Video/Graphics Processor.

The PS/2 writes 16-bit data to the Data Bus Interface which latches four consecutive PS/2 data write transfers to form one 64-bit data word. Upon receipt of the fourth transfer, it writes the 64-bit word to the Dynamic RAM.

The 64-bit data read from the Dynamic RAM may be either graphics or image data. Graphics data is latched and output to the Video/Graphics Processor via the 64-bit Graphics Data bus. Image data is output directly (unlatched) to the Video/Graphics Processor via the 64-bit Image Data bus.

## **RAM Timing Generator**

The RAM Timing Generator:

- generates all Dynamic RAM read, write, address multiplexer controls and chip selects

- · performs the Dynamic RAM refresh cycles

- · generates the video and graphics latch strobes

- decodes and latches the pixel select addresses

- generates RAM access cycle control signals such as WDE (Write Data Enable), GRE (Graphics Read Enable - used by U10), and XWDE (External Write Data Enable - used by U10)

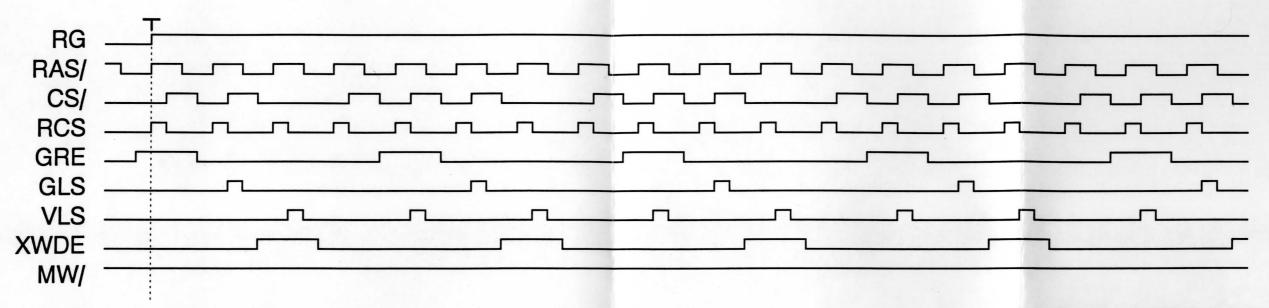

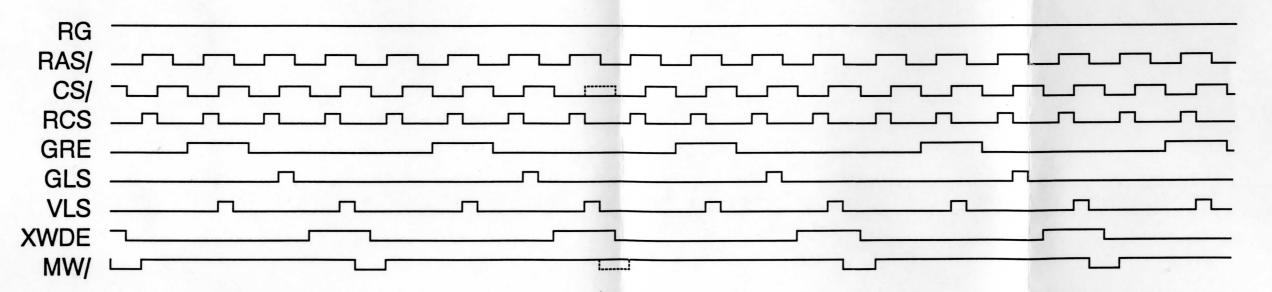

Dynamic RAM reading, writing and refresh occurs within a fixed RAM access timing cycle. The diagram below shows this cycle. Dynamic RAM refreshing is accomplished during the Write Opportunity phase if there is no data to be written into the Dynamic RAM. Each phase in the diagram below is four pixel clock periods in duration (about 160 nanoseconds).

Graphics Image Write Image Read Opportunity Read

The Video and Graphics Latch Strobes (VLS and GLS, respectively latch the 64-bit image and graphics data words, respectively. The graphics latches are located in the Data Bus Interface; the image latches are part of the Video/Graphics Processor.

The Pixel Select Address is a 4-bit address that points to the pixel within a 64-bit word address. Only the three LSBs are required to address the image byte (0-7 range). However, all four bits are required to select the current graphics nibble (0-15p range).

The first image or graphics pixel in a horizontal line does not always start with the first byte or nibble in a 64-bit word. As an example, suppose the SDA is operating in a zoom factor of 4. Remember that a zoom factor of 1 requires eighty 8-byte (640 bytes total) image words or forty 16-nibble graphics words to display a horizontal line of video or graphics, respectively. A zoom factor of 4 requires only 160 image bytes or graphics nibbles because each pixel (byte or nibble) is repeated four times. Thus, twenty 8-byte image or ten 16-nibble graphics words are required if each byte or nibble is used. Suppose the user roams one pixel to the right. To accomplish this, the memory read logic will retrieve the first word, but the first pixel (byte or nibble) must be discarded. This is done by using the Start Point input to the RAM Timing Generator to preset the Pixel Select Address to a count of one. This causes it to point at the second image byte and graphics nibble. The SDA will display that pixel and each of the remaining pixels in the first word four times each. Each pixel of the next 19 image and/or 9 graphics words is displayed four times each. At this point, 636 pixels have been painted. To display the last four pixels, the next word must be read (twenty-first image word and/or eleventh graphics word); only the first pixel is used and replicated four times.

To summarize, the Start Point address is used only to preset the Pixel Select Address counter to the pixel address of the first pixel in the first word of each horizontal line. For the remainder of each line, the Start Point has no effect. The total number of bytes or nibbles used per horizontal line is always 640/(Zoom Factor). Finally, some pixels in the first and last words fetched for a horizontal line may not be used when roaming.

<sup>\*</sup> RAM refresh is performed during this time if there is no Write data ready for transfer to the RAM.

### **Command Latch**

The SDA requires the following control information before it can display an image:

- Relative Start Address (19 bits)

- Zoom Factor (3 bits)

- Video Frame Start Address (9 MSB bits)

- Graphics Frame Start Address (9 MSB bits)

- Graphics Mask (4 bits)

The above information is called *command data* and is packed into four concatenated 16-bit words.

The division of functions between U9 and U10 causes both chips to require some or all of the command data. Currently, the PS/2 writes this data to addresses XXE00008H - XXE0000FH (subject to change, "XX" is defined by A24 - A31), causing the Micro Channel Interface chip to assert CWD/ (Command Word). If CWD/ is a result of a 16-bit memory write, U10 asserts CWS/ (Command Word Strobe). CWS/ is used internally by U10 and is also exported to U9.

CWS/ strobes the Command Latch in U9. LA1 - LA2 (second and third LSB latched Address bits) identify the data on the OD bus. Internal latches, qualified by LA1 and LA2, latch the appropriate OD bus bits on the trailing rising edge of CWS/.

The RAM Timing Generator uses the Zoom Factor to determine the pixel replication number, and thus, the Dynamic RAM read rate. It uses Start Point to determine the start pixel in the first word of each horizontal line.

The Graphics Mask is required by the Video/Graphics Processor to determine which graphics bit planes are displayed.

#### **Video/Graphics Processor**

The Video/Graphics Processor disassembles 64-bit image and graphics words into bytes and nibbles, respectively, and transfers them to the RAMDACs at the pixel clock rate.

The Pixel Select Address input points at the current image and graphics pixel data within the respective 64-bit word; the Graphics Mask input determines which graphics bit planes are active. The Cursor input causes the Video/Graphics Processor to set Graphics bits G0 - G3, the Graphics Flag, and Image Data bits V0 - V3 high.

Issued 6/92 25

Figure 5. U10 Functional Block Diagram

# U10 Functional Description

The U10 Functional Description is based on Figure 5 shown on the adjacent page. U10 contains the following functional blocks:

- Timing Generator

- Address Strobe Generator

- RAM Read/Write Addressing

- Address Input Latch

- RAMDAC Byte Selector

- Interlace Generator